# 亮点

- 高性价比的以太网物理层收发器(PHY)

- 可变I/O电压范围: +1.6V至+3.6V

- 集成1.2V稳压器

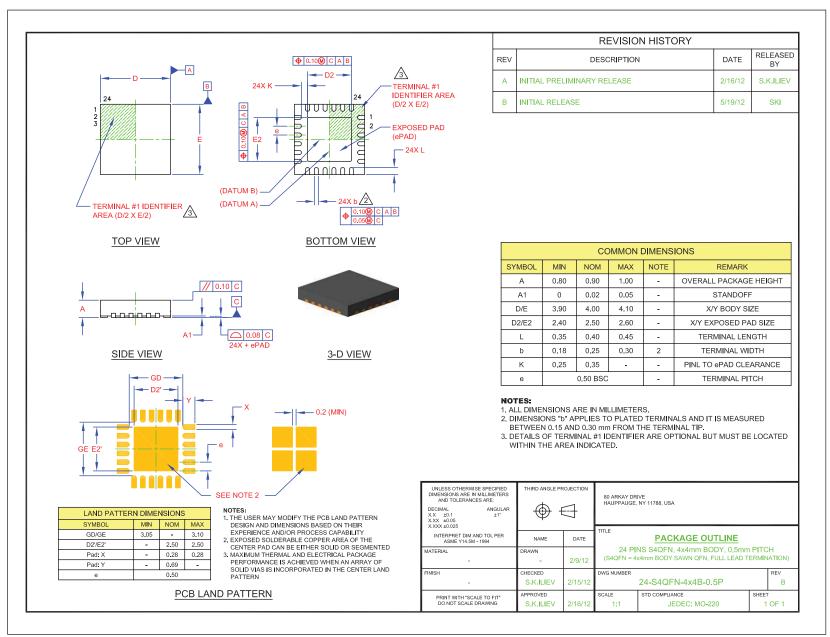

- 符合RoHS标准的小型24引脚SQFN无铅封装(4x4mm)

# 目标应用

- 机顶盒

- 网络打印机和服务器

- 测试仪表

- 板载网卡

- 嵌入式电信应用

- 视频录制/播放系统

- 线缆调制解调器/路由器

- DSL调制解调器/路由器

- 数字录像机

- IP和视频电话

- 无线接入点

- 数字电视

- 数字媒体适配器/服务器

- 游戏机

- POE应用

# 主要优势

- 10/100以太网收发器

- 符合IEEE802.3/802.3u(快速以太网)

- 符合ISO 802-3/IEEE 802.3(10BASE-T)

- 环回模式

- 自动协商

- 自动极性检测和校正

- 链路状态变化唤醒检测

- 供应商特定寄存器功能

- 支持低引脚数的RMII接口

- 电源和I/O

- 各种低功耗模式

- 集成上电复位电路

- 两个状态LED输出

- 可在3.3V单电源供电下使用

- 其他特性

- 可使用低成本的25 MHz晶振,从而降低BOM成本

- 封装

- 符合RoHS标准的24引脚SQFN(4x4mm)无铅封装,带RMII

- 环境

- 扩展商业级温度范围(0°C至+85°C)

# 目录

| 亮点  | î    |                 | 1  |

|-----|------|-----------------|----|

| 日梅  | 田物   |                 | 1  |

|     |      |                 |    |

| 主要  | 【优势… |                 | 1  |

| 1.0 | 简介   |                 | 4  |

|     | 1.1  | 通用术语和约定         | 4  |

|     | 1.2  | 概述              | 4  |

| 2.0 | 引脚说  | .明和配置           | 6  |

|     | 2.1  | 引脚分配            | 12 |

|     | 2.2  | 缓冲器类型           | 12 |

| 3.0 | 功能说  | .明              | 14 |

|     | 3.1  | 收发器             |    |

|     | 3.2  | 自动协商            |    |

|     | 3.3  |                 |    |

|     | 3.4  | MAC接口           |    |

|     | 3.5  | 串行管理接口(SMI)     | 23 |

|     | 3.6  | 中断管理            | 24 |

|     | 3.7  | 配置脚             | 26 |

|     | 3.8  | 其他功能            | 31 |

|     | 3.9  | 应用图             | 35 |

| 4.0 | 寄存器  | <del>-</del> 说明 | 40 |

|     | 4.1  | 寄存器命名法          | 40 |

|     | 4.2  | 控制和状态寄存器        | 40 |

| 5.0 | 工作特  | ·性              | 50 |

|     | 5.1  | 绝对最大额定值*        | 50 |

|     | 5.2  | 工作条件**          |    |

|     | 5.3  | <b>封装热规范</b>    |    |

|     | 5.4  | 功耗              | 51 |

|     | 5.5  | 直流规范            | 52 |

|     | 5.6  | 交流规范            | 55 |

|     | 5.7  | 时钟电路            | 61 |

| 6.0 | 封装信  | 息               | 64 |

|     | 6.1  | 24-SQFN(锯切)     | 64 |

| 7.0 | 应用说  | .明              | 65 |

|     | 7.1  | 应用图             |    |

|     |      |                 | ٧  |

| 产品标识体系 | 67 |

|--------|----|

| 制造商信息  | 68 |

# 1.0 简介

# 1.1 通用术语和约定

下面列出了本文档中使用的通用术语:

| ВҮТЕ     | 8位                                                                                          |

|----------|---------------------------------------------------------------------------------------------|

| FIFO     | 先进先出缓冲区;通常用于实现弹性缓冲功能                                                                        |

| MAC      | 介质访问控制器                                                                                     |

| RMII™    | 精简的介质无关接口(Reduced Media Independent Interface)                                              |

| N/A      | 不适用                                                                                         |

| х        | 表示逻辑状态为"无关"或未定义。                                                                            |

| RESERVED | 指保留的位域或地址。除非另外说明,否则对于写操作,保留的位必须始终为零。<br>除非另外说明,否则在读取保留位时无法保证值。除非另外说明,否则请勿对保留<br>的地址进行读或写操作。 |

| SMI      | 串行管理接口                                                                                      |

## 1.2 概述

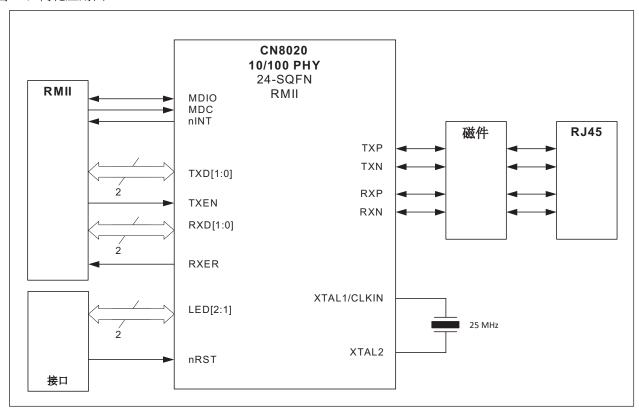

CN8020是一款高性价比的具有可变I/O电压的10BASE-T/100BASE-TX物理层(PHY)收发器,符合IEEE 802.3-2005标准。

CN8020支持通过标准RMII接口与以太网MAC进行通信。它包含一个全双工10-BASE-T/100BASE-TX收发器,支持 10 Mbps(10BASE-T)和100 Mbps(100BASE-TX)工作模式。CN8020可实现自动协商以自动确定可能的最佳速度以及双工工作模式。

CN8020支持符合IEEE 802.3-2005标准和供应商特定的寄存器功能。但是,工作时不需要访问寄存器。初始配置可通过配置引脚来选择,如第1.1节"通用术语和约定"(第4页)所述。通过寄存器可以选择一些配置选项,以此进一步定义收发器的功能。

根据IEEE 802.3-2005标准,所有数字接口引脚均可承受3.6V电压。利用集成的3.3V转1.2V线性稳压器,可以将该器件配置为在3.3V单电源的供电下运行。可以有选择地禁止线性稳压器,从而允许使用高效率的外部稳压器来降低系统功耗。

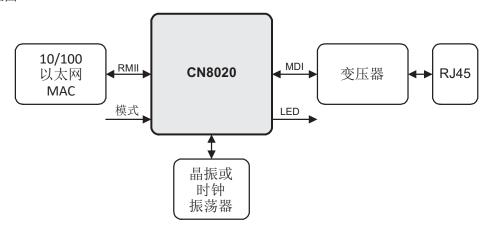

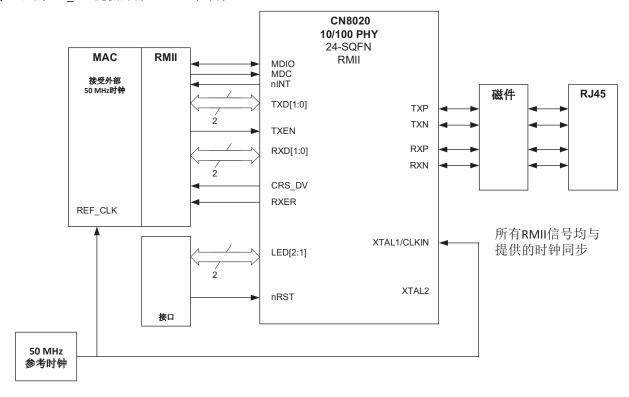

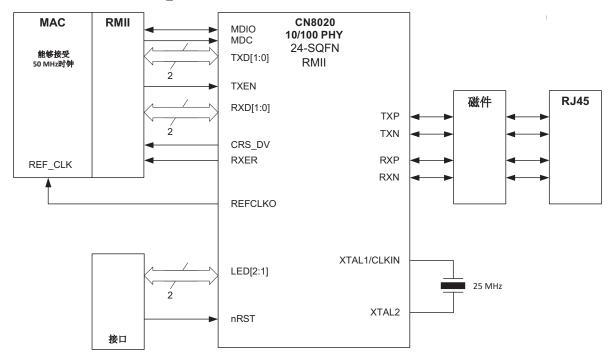

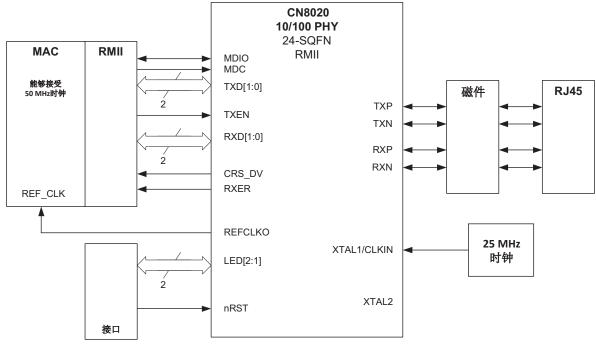

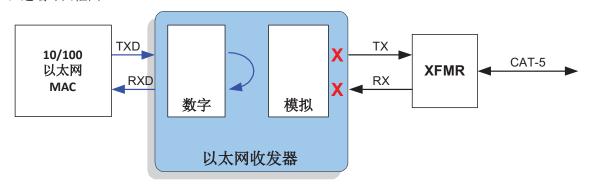

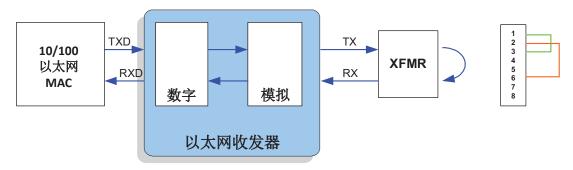

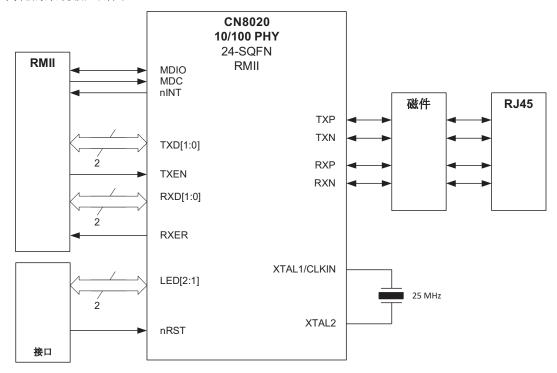

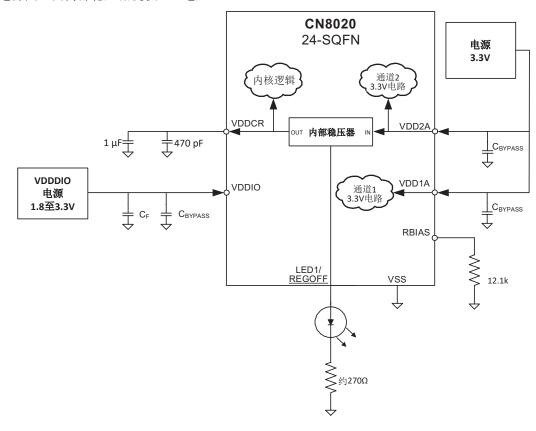

CN8020可在扩展商业级温度范围内使用。图1-1显示了典型的系统应用。

#### 图1-1: 系统框图

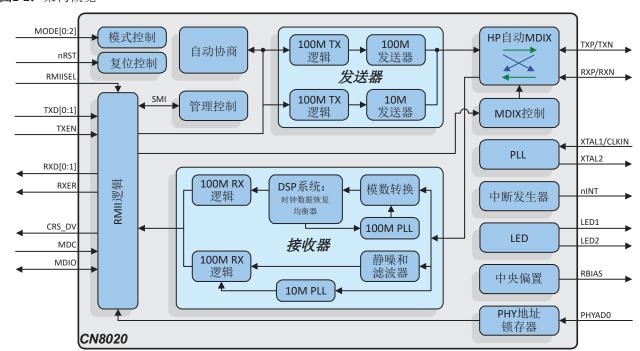

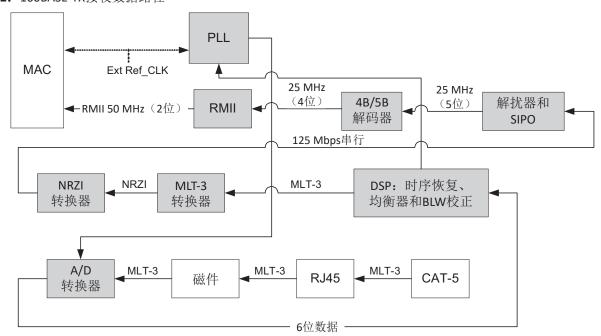

## 图1-2: 架构概览

# 2.0 引脚说明和配置

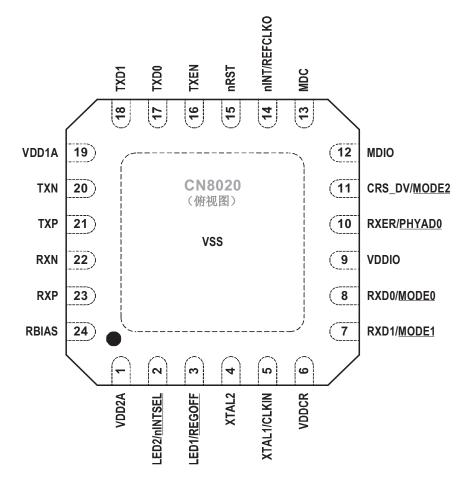

图2-1: 24-SQFN引脚分配 (俯视图)

- 注: 封装底部的外露焊盘(VSS)必须接地

- **注2-1** 当信号名称开头使用小写字母"n"时,表示该信号低电平有效。例如,nRST表示该复位信号低电平有效。

- 注2-2 "缓冲器类型"列中给出了每个信号的缓冲器类型。第2.2节提供了缓冲器类型的说明。

# **表2-1:** RMII信号

| 引脚编号 | 名称              | 符号     | 缓冲器<br>类型   | 说明                                                    |

|------|-----------------|--------|-------------|-------------------------------------------------------|

| 1    | 发送数据0           | TXD0   | VIS         | MAC使用该信号将数据发送到收发器。                                    |

| 1    | 发送数据1           | TXD1   | VIS         | MAC使用该信号将数据发送到收发器。                                    |

| 1    | 发送使能            | TXEN   | VIS<br>(PD) | 指示TXD[1:0]上存在有效的发送数据。                                 |

| 1    | 接收数据0           | RXD0   | VO8         | 收发器在接收路径上发送的2个数据位的bit 0。                              |

|      | PHY工作模式0<br>配置脚 | MODE0  | VIS<br>(PU) | 该配置脚搭配MODE1和MODE2用于设置默认PHY模式。                         |

|      |                 |        |             | 有关配置脚的更多信息,请参见注2-3。                                   |

|      |                 |        |             | 注: 更多详细信息,请参见第3.7.2节 "MODE [2:0]: 模式配置" (第27页)。       |

| 1    | 接收数据1           | RXD1   | VO8         | 收发器在接收路径上发送的2个数据位的bit 1。                              |

|      | PHY工作模式1<br>配置脚 | MODE1  | VIS<br>(PU) | 该配置脚搭配MODE0和MODE2用于设置默认PHY模式。                         |

|      |                 |        |             | 有关配置脚的更多信息,请参见注2-3。                                   |

|      |                 |        |             | 注: 更多详细信息,请参见第3.7.2节"MODE [2:0]:模式配置"(第27页)。          |

| 1    | 接收错误            | RXER   | VO8         | 该信号置为有效时表示在当前从收发器传输的帧中 检测到错误。                         |

|      | PHY地址0<br>配置脚   | PHYAD0 | VIS<br>(PD) | 该配置脚用于设置收发器的SMI地址。                                    |

|      |                 |        |             | 有关配置脚的更多信息,请参见注2-3。                                   |

|      |                 |        |             | <b>注:</b> 更多信息,请参见第3.7.1节 "PHYAD[0]: PHY 地址配置"(第26页)。 |

**表2-1:** RMII信号(续)

| 引脚编号 | 名称              | 符号     | 缓冲器<br>类型   | 说明                                                                                                                                   |

|------|-----------------|--------|-------------|--------------------------------------------------------------------------------------------------------------------------------------|

| 1    | 载波侦听/接收<br>数据有效 | CRS_DV | VO8         | 该信号置为有效时表示接收介质处于非空闲状态。<br>当接收到10BASE-T数据包时,CRS_DV置为有效,但<br>RXD[1:0]保持低电平,直到接收到SFD字节<br>(10101011)为止。<br>注: 根据RMII标准,在10BASE-T半双工模式下, |

|      |                 |        |             | 发送的数据不环回到接收数据引脚。                                                                                                                     |

|      | PHY工作模式2<br>配置脚 | MODE2  | VIS<br>(PU) | 该配置脚搭配MODE0和MODE1用于设置默认PHY模式。                                                                                                        |

|      |                 |        |             | 有关配置脚的更多信息,请参见注2-3。                                                                                                                  |

|      |                 |        |             | 注: 更多详细信息,请参见第3.7.2节"MODE [2:0]:模式配置"(第27页)。                                                                                         |

**注2-3** 配置脚值在上电复位和系统复位时锁存。配置脚由带下划线的符号名称标识。连接负载时,用作配置脚的信号必须增加一个外部电阻。更多信息,请参见第3.7节"配置脚"(第26页)。

表2-2: LED引脚

| 引脚编号 | 名称           | 符号     | 缓冲器<br>类型  | 说明                                                                                      |

|------|--------------|--------|------------|-----------------------------------------------------------------------------------------|

|      | LED 1        | LED1   | 012        | 链路活动LED指示。该引脚在检测到有效链路时驱动<br>为有效状态,在检测到活动时闪烁。                                            |

|      |              |        |            | <b>注:</b> 有关LED的更多信息,请参见第3.8.1节 "LED" (第31页)。                                           |

|      | 稳压器关闭<br>配置脚 | REGOFF | IS<br>(PD) | 该配置脚用于禁止内部1.2V稳压器。禁止稳压器时,<br>必须向VDDCR提供外部1.2V电压。                                        |

| 1    |              |        |            | <ul> <li>当REGOFF通过外部电阻拉高至VDD2A时,禁止内部稳压器。</li> <li>当REGOFF悬空或拉低时,使能内部稳压器(默认)。</li> </ul> |

|      |              |        |            | 有关配置脚的更多信息,请参见注2-4。                                                                     |

|      |              |        |            | 注: 更多详细信息,请参见第3.7.3节 "REGOFF:<br>内部+1.2V稳压器配置" (第28页)。                                  |

表2-2: LED引脚(续)

| 引脚编号 | 名称                          | 符号      | 缓冲器<br>类型  | 说明                                                                                                                                                     |

|------|-----------------------------|---------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | LED 2                       | LED2    | 012        | 链路速度LED指示。当工作速度为100 Mbps时,该引脚将驱动为有效状态。当工作速度为10 Mbps时,或者线路隔离期间,该引脚处于无效状态。                                                                               |

|      |                             |         |            | <b>注:</b> 有关LED的更多信息,请参见第3.8.1节 "LED" (第31页)。                                                                                                          |

| 1    | nINT/REFCLKO<br>功能选择<br>配置脚 | nINTSEL | IS<br>(PU) | 该配置脚用于选择nINT/REFCLKO引脚的模式。  • 当 <u>nINTSEL</u> 悬空或拉至VDD2A时,在nINT/REFCLKO引脚上选择nINT工作模式(默认)。  • 当 <u>nINTSEL</u> 被拉低至VSS时,在nINT/REFCLKO引脚上选择REFCLKO工作模式。 |

|      |                             |         |            | 有关配置脚的更多信息,请参见注2-4。                                                                                                                                    |

|      |                             |         |            | <b>注:</b> 更多信息,请参见第3.8.1.2节"nINTSEL和 LED2极性选择"(第31页)。                                                                                                  |

**注2-4** 配置脚值在上电复位和系统复位时锁存。配置脚由带下划线的符号名称标识。连接负载时,用作配置脚的信号必须增加一个外部电阻。更多信息,请参见第3.7节"配置脚"(第26页)。

表2-3: 串行管理接口(SMI)引脚

| 引脚编号 | 名称             | 符号   | 缓冲器<br>类型 | 说明            |

|------|----------------|------|-----------|---------------|

| 1    | SMI数据输入/<br>输出 | MDIO | VIS/VOD8  | 串行管理接口数据输入/输出 |

| 1    | SMI时钟          | MDC  | VIS       | 串行管理接口时钟      |

### 表2-4: 以太网引脚

| 引脚编号 | 名称               | 符号  | 缓冲器<br>类型 | 说明        |

|------|------------------|-----|-----------|-----------|

| 1    | 以太网TX/RX<br>正通道1 | ТХР | AIO       | 发送/接收正通道1 |

| 1    | 以太网TX/RX<br>负通道1 | TXN | AIO       | 发送/接收负通道1 |

### 表2-4: 以太网引脚(续)

| 引脚编号 | 名称               | 符号  | 缓冲器<br>类型 | 说明        |

|------|------------------|-----|-----------|-----------|

| 1    | 以太网TX/RX<br>正通道2 | RXP | AIO       | 发送/接收正通道2 |

| 1    | 以太网TX/RX<br>负通道2 | RXN | AIO       | 发送/接收负通道2 |

# **表2-5:** 其他引脚

| 引脚编号 | 名称     | 符号      | 缓冲器<br>类型    | 说明                                                                                                                                                                    |

|------|--------|---------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | 外部晶振输入 | XTAL1   | ICLK         | 外部晶振输入                                                                                                                                                                |

|      | 外部时钟输入 | CLKIN   | ICLK         | 单端时钟振荡器输入。<br>注: 使用单端时钟振荡器时,不得连接XTAL2。                                                                                                                                |

| 1    | 外部晶振输出 | XTAL2   | OCLK         | 外部晶振输出                                                                                                                                                                |

| 1    | 外部复位   | nRST    | VIS<br>(PU)  | 系统复位。该信号低电平有效。                                                                                                                                                        |

| 1    | 中断输出   | nINT    | VOD8<br>(PU) | 低电平有效中断输出。放置一个上拉至VDDIO的外部电阻。 注: 有关器件中断的更多详细信息,请参见第3.6节"中断管理"(第24页)。 注: 有关如何使用 <u>nINTSEL</u> 配置脚来确定该引脚功能的详细信息,请参见第3.8.1.2节"nINTSEL和LED2极性选择"(第31页)。                   |

|      | 参考时钟输出 | REFCLKO | VO8          | 该50 MHz时钟输出为可选项,源自25 MHz晶振。REFCLKO可通过nINTSEL配置脚来选择。 注: 更多详细信息,请参见第3.7.4.2节"REF_CLK输出模式"(第29页)。 注: 有关如何使用nINTSEL配置脚来确定该引脚功能的详细信息,请参见第3.8.1.2节"nINTSEL和LED2极性选择"(第31页)。 |

# 表2-6: 模拟参考引脚

| 引脚编号 | 名称             | 符号    | 缓冲器<br>类型 | 说明                          |

|------|----------------|-------|-----------|-----------------------------|

| 1    | 外部1%偏置<br>电阻输入 | RBIAS | Al        | 该引脚需要通过12.1 kΩ(1%)电阻接地。     |

|      | 10月11117人      |       |           | 有关连接信息,请参见CN8020参考原理图。      |

|      |                |       |           | 注: 标称电压为1.2V,电阻消耗的功率约为1 mW。 |

# **表2-7:** 电源引脚

| 引脚编号 | 名称                     | 符号    | 缓冲器<br>类型 | 说明                                           |

|------|------------------------|-------|-----------|----------------------------------------------|

| 1    | +1.6V到+3.6V<br>可变I/O电源 | VDDIO | Р         | +1.6V到+3.6V可变I/O电源                           |

|      |                        |       |           | 有关连接信息,请参见CN8020参考原理图。                       |

| 1    | +1.2V数字内核<br>电源        | VDDCR | Р         | 除非通过 <u>REGOFF</u> 配置脚配置为稳压器关闭模式,否则由片上稳压器供电。 |

|      |                        |       |           | 有关连接信息,请参见CN8020参考原理图。                       |

|      |                        |       |           | 注: 应在该引脚上使用并联接地的1 μF和470 pF去<br>耦电容。         |

| 1    | +3.3V通道1<br>模拟端口电源     | VDD1A | Р         | 通道1的+3.3V模拟端口电源                              |

|      |                        |       |           | 有关连接信息,请参见CN8020参考原理图。                       |

| 1    | +3.3V通道2<br>模拟端口电源     | VDD2A | Р         | 通道2和内部稳压器的+3.3V模拟端口电源。                       |

|      |                        |       |           | 有关连接信息,请参见CN8020参考原理图。                       |

| 1    | 地                      | VSS   | Р         | 公共地。此外露焊盘必须通过过孔阵列连接到地<br>平面。                 |

# 2.1 引脚分配

表2-8: 24-SQFN封装引脚分配

| 引脚编号 | 引脚名称                 | 引脚编号 | 引脚名称         |

|------|----------------------|------|--------------|

| 1    | VDD2A                | 13   | MDC          |

| 2    | LED2/ <u>nINTSEL</u> | 14   | nINT/REFCLKO |

| 3    | LED1/ <u>REGOFF</u>  | 15   | nRST         |

| 4    | XTAL2                | 16   | TXEN         |

| 5    | XTAL1/CLKIN          | 17   | TXD0         |

| 6    | VDDCR                | 18   | TXD1         |

| 7    | RXD1/ <u>MODE1</u>   | 19   | VDD1A        |

| 8    | RXD0/ <u>MODE0</u>   | 20   | TXN          |

| 9    | VDDIO                | 21   | TXP          |

| 10   | RXER/ <u>PHYAD0</u>  | 22   | RXN          |

| 11   | CRS_DV/ <u>MODE2</u> | 23   | RXP          |

| 12   | MDIO                 | 24   | RBIAS        |

# 2.2 缓冲器类型

表2-9: 缓冲器类型

| 缓冲器类型 | 说明                                                                   |

|-------|----------------------------------------------------------------------|

| IS    | 施密特触发输入                                                              |

| 012   | 具有12 mA灌/拉电流能力的输出                                                    |

| VIS   | 电压可变的施密特触发输入                                                         |

| VO8   | 具有8 mA灌/拉电流能力的可变电压输出                                                 |

| VOD8  | 具有8 mA灌电流能力的可变电压漏极开路输出                                               |

| PU    | 50 μA (典型值)内部上拉。除非引脚说明中另外说明,否则始终使能内部上拉。                              |

|       | <b>注:</b> 内部上拉电阻用于防止未连接输入悬空。请勿依靠内部电阻来驱动器件外部的信号。连接到必须拉高的负载时,必须添加外部电阻。 |

| PD    | 50 μA (典型值)内部下拉。除非引脚说明中另外说明,否则始终使能内部下拉。                              |

|       | <b>注:</b> 内部下拉电阻用于防止未连接输入悬空。请勿依靠内部电阻来驱动器件外部的信号。连接到必须拉低的负载时,必须添加外部电阻。 |

| Al    | 模拟输入                                                                 |

| AIO   | 模拟双向                                                                 |

| ICLK  | 晶振输入引脚                                                               |

| OCLK  | 晶振输出引脚                                                               |

| Р     | 电源引脚                                                                 |

- **注2-5** 数字信号不能承受5V的电压。有关缓冲器的更多信息,请参见第5.1节"绝对最大额定值\*" (第50页)。

- **注2-6** 灌/拉电流能力取决于VDDIO电压。更多信息,请参见第5.1节"绝对最大额定值\*"(第50页)。

# 3.0 功能说明

本章提供器件各种特性的功能说明。这些特性按照类别分为以下几个部分:

- 收发器

- 自动协商

- 支持HP自动MDIX

- MAC接口

- 串行管理接口(SMI)

- 中断管理

- 配置脚

- 其他功能

- 应用图

# 3.1 收发器

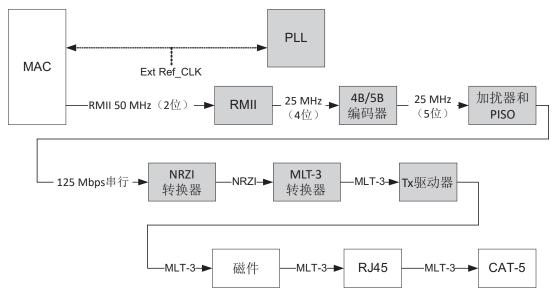

#### 3.1.1 100BASE-TX发送

图3-1给出了100BASE-TX发送数据路径。其中的主要模块将在后续几个小节中逐一介绍。

图3-1: 100BASE-TX发送数据路径

#### 3.1.1.1 通过RMII接口传输的100BASE-TX发送数据

MAC控制器将发送数据驱动到TXD总线上,并将TXEN置为有效以指示数据有效。该数据由收发器的RMII模块在REF CLK的上升沿锁存。该数据为2位宽格式的50 MHz数据。

#### 3.1.1.2 4B/5B编码

发送数据从RMII模块传递到4B/5B编码器。编码器模块根据表3-1将数据从4位半字节编码为5位符号(称为"代码组")。每个4位数据半字节都映射到32个可能的代码组中的16个。其余16个代码组用于控制信息或者无效。前16个代码组由其对应的数据半字节的十六进制值(从0到F)表示。其余代码组由两侧带有斜杠的字母表示。例如,空闲代码组为/I/,发送错误代码组为/H/等。

表3-1: 4B/5B代码表

| 代码组   | 符号 |                   | 接收器解释                                       |      |          | 发送器解释    |      |  |  |

|-------|----|-------------------|---------------------------------------------|------|----------|----------|------|--|--|

| 11110 | 0  | 0                 | 0000                                        | DATA | 0        | 0000     | DATA |  |  |

| 01001 | 1  | 1                 | 0001                                        | _    | 1        | 0001     | _    |  |  |

| 10100 | 2  | 2                 | 0010                                        | _    | 2        | 0010     | _    |  |  |

| 10101 | 3  | 3                 | 0011                                        | _    | 3        | 0011     | _    |  |  |

| 01010 | 4  | 4                 | 0100                                        | _    | 4        | 0100     | _    |  |  |

| 01011 | 5  | 5                 | 0101                                        | _    | 5        | 0101     | _    |  |  |

| 01110 | 6  | 6                 | 0110                                        | _    | 6        | 0110     | _    |  |  |

| 01111 | 7  | 7                 | 0111                                        | _    | 7        | 0111     | _    |  |  |

| 10010 | 8  | 8                 | 1000                                        | _    | 8        | 1000     | _    |  |  |

| 10011 | 9  | 9                 | 1001                                        | _    | 9        | 1001     | _    |  |  |

| 10110 | А  | А                 | 1010                                        | _    | А        | 1010     | _    |  |  |

| 10111 | В  | В                 | 1011                                        | _    | В        | 1011     | _    |  |  |

| 11010 | С  | С                 | 1100                                        | _    | С        | 1100     | _    |  |  |

| 11011 | D  | D                 | 1101                                        | _    | D        | 1101     | _    |  |  |

| 11100 | E  | E                 | 1110                                        | _    | Е        | 1110     | _    |  |  |

| 11101 | F  | F                 | 1111                                        | _    | F        | 1111     | _    |  |  |

| 11111 | I  | 空闲                |                                             |      | /T/R后发送, | 直到接收到TXI | EN   |  |  |

| 11000 | J  |                   | SSD的第一个半字节,空闲后转换为<br>"0101",否则为RXER         |      |          | 时发送      |      |  |  |

| 10001 | K  |                   | SSD的第二个半字节,在J后转换为<br>"0101",否则为RXER         |      |          | 时发送      |      |  |  |

| 01101 | Т  |                   | ESD的第一个半字节,后跟/R/时会导致<br>CRS置为无效,否则将RXER置为有效 |      |          | 时发送      |      |  |  |

| 00111 | R  |                   | 半字节,在/T/<br>列将RXER置为                        |      | TXEN下降沿  | 时发送      |      |  |  |

| 00100 | Н  | 发送错误符号            | L<br>i                                      |      | TXER上升沿时 | ·<br>时发送 |      |  |  |

| 00110 | V  | 无效, <b>RXDV</b> 期 | 阴间为RXER                                     |      | 无效       |          |      |  |  |

| 11001 | V  | 无效, <b>RXDV</b> 其 | 无效,RXDV期间为RXER                              |      |          |          |      |  |  |

| 00000 | V  | 无效, <b>RXDV</b> 其 | 无效,RXDV期间为RXER                              |      |          |          |      |  |  |

| 00001 | V  | 无效, <b>RXDV</b> 其 | 无效,RXDV期间为RXER                              |      |          |          |      |  |  |

| 00010 | V  | 无效, <b>RXDV</b> 期 | 无效,RXDV期间为RXER                              |      |          |          |      |  |  |

| 00011 | V  | 无效,RXDV期          | 无效,RXDV期间为RXER                              |      |          |          |      |  |  |

| 00101 | V  | 无效, <b>RXDV</b> 其 | 无效,RXDV期间为RXER                              |      |          |          |      |  |  |

| 01000 | V  | 无效,RXDV其          | 无效,RXDV期间为RXER                              |      |          |          |      |  |  |

| 01100 | V  | 无效,RXDV其          | 无效,RXDV期间为RXER                              |      |          |          |      |  |  |

| 10000 | V  | 工並 1000/世         | 无效,RXDV期间为RXER                              |      |          |          |      |  |  |

#### 3.1.1.3 加扰

重复的数据模式(特别是空闲代码组)会导致功率谱密度中存在很大的窄带峰值。对数据加扰有助于消除这些峰值并在整个通道带宽上更均匀地分布信号功率。FCC法规要求采用这种统一的谱密度以避免物理接线产生过多的FMI。

加扰器的种子由收发器地址(PHYAD)产生,确保多收发器应用(例如中继器或交换机)中的每个收发器都有自己的加扰器序列。

加扰器还会对数据执行并行输入串行输出(Parallel In Serial Out,PISO)转换。

#### 3.1.1.4 NRZI和MLT-3编码

加扰器模块将5位宽的并行数据传递到NRZI转换器,数据将在该转换器中变为串行125 MHz NRZI数据流。然后将NRZI编码为MLT-3。MLT-3是一种三电平代码,其中代码位1表示逻辑电平发生变化,代码位0表示没有变化。

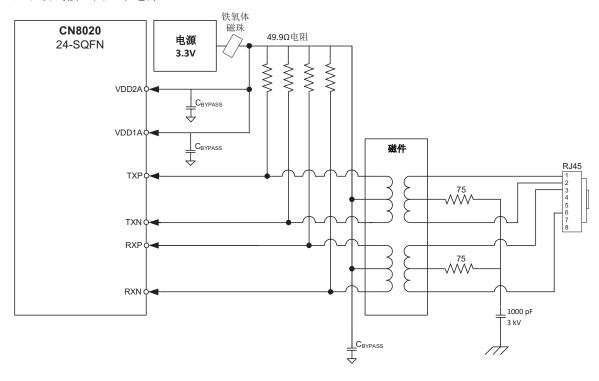

#### 3.1.1.5 100M发送驱动器

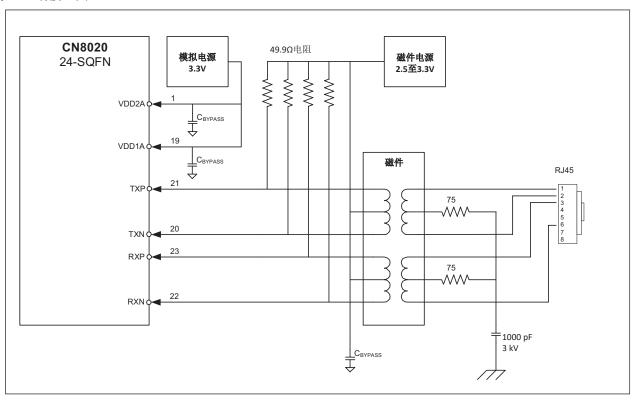

MLT3数据随后会传递到模拟发送器,该发送器将输出引脚TXP和TXN上的差分MLT-3信号驱动到1:1比例隔离变压器两端的双绞线介质中。10BASE-T和100BASE-TX信号通过同一个变压器传递,因此可以对两个信号共用一个"磁件"。发送器驱动到CAT-5线缆的100Ω阻抗中。线缆端接和阻抗匹配需要外部元件。

#### 3.1.1.6 100M锁相环(PLL)

100M锁相环(Phase Lock Loop,PLL)锁定到参考时钟并生成用于驱动125 MHz逻辑和100BASE-TX发送器的125 MHz 时钟。

#### 3.1.2 100BASE-TX接收

图3-2给出了100BASE-TX接收数据路径。其中的主要模块将在后续几个小节中逐一介绍。

#### **图3-2:** 100BASE-TX接收数据路径

### 3.1.2.1 100M接收输入

来自线缆的MLT-3数据通过1:1比例变压器馈入收发器(在输入RXP和RXN上)。ADC以每秒125M个采样的速率对传入的差分信号进行采样。利用64级量化器,生成6个数字位以代表每个采样。DSP根据观测到的信号电平调整ADC的增益,以便使用ADC的整个动态范围。

#### 3.1.2.2 均衡器、基线漂移校正和时钟/数据恢复

将ADC的6位馈入DSP模块。DSP部分中的均衡器用于补偿由磁件、连接器和CAT-5线缆组成的物理通道引起的相位和幅值失真。均衡器可以为长度在1m到150m之间的高品质CAT-5线缆恢复信号。

如果信号的直流成分使低频分量降至隔离变压器的低频极点以下,则变压器的下垂特性会明显增强,并将在接收的信号上产生基线漂移(Baseline Wander,BLW)。为避免接收的数据损坏,收发器会针对BLW进行校正并可接收ANSI X3.263-1995 FDDI TP-PMD定义的无位错误的"杀手包"(killer packet)。

100M PLL生成125 MHz时钟的多个相位。由DSP定时单元控制的多路开关会选择最佳相位以对数据进行采样。此时钟被用作接收的恢复时钟。此时钟用于从接收的信号中提取串行数据。

#### 3.1.2.3 NRZI和MLT-3解码

DSP生成馈入MLT-3转换器的MLT-3恢复电平。MLT-3随后会转换为NRZI数据流。

#### 3.1.2.4 解批

解扰器执行与发送器中的加扰器相反的功能,还会对数据执行串行输入并行输出(Serial In Parallel Out,SIPO)转换。

在接收空闲(/I/)符号期间,解扰器将其解扰密钥与传入的流同步。同步完成后,解扰器会锁定此密钥,并且 能够解扰传入的数据。

解扰器中的特殊逻辑通过在4000字节(40 μs)的窗口中搜索空闲符号来确保与远程收发器同步。该窗口确保可以无干扰地接收符合IEEE 802.3标准、大小不超过1514字节的数据包。如果在该时间段内未检测到空闲符号,则接收操作将中止,解扰器将重启同步过程。

#### 3.1.2.5 对齐方式

之后,通过在数据包的起始部分识别/J/K/流起始分隔符(Start-of-Stream Delimiter,SSD)对,将解扰后的信号对齐到5位代码组。确定码字对齐后,将存储和使用该码字,直到下一帧开始。

#### 3.1.2.6 5B/4B解码

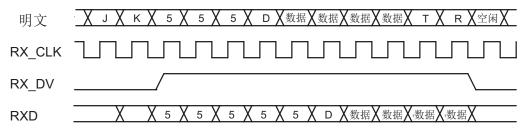

根据4B/5B表将5位代码组转换为4位数据半字节。转换后的数据出现在RXD[1:0]信号线上。SSD(/J/K/)转换为"0101 0101",作为MAC前导码的前2个半字节。接收到SSD后,收发器会将接收数据有效信号置为有效,指示在RXD总线上存在有效数据。连续的有效代码组将转换为数据半字节。在收到由/T/R/符号组成的流结束分隔符(End of Stream Delimiter,ESD)或至少两个/I/符号后,收发器会将载波侦听和接收数据有效信号置为无效。

注: 这些符号不会转换为数据。

#### 3.1.2.7 接收数据有效信号

接收数据有效信号(RXDV)指示与RXCLK同步的RXD[1:0]输出上出现已恢复和解码的半字节。RXDV在识别到/J/K/分隔符后变为有效,RXD与半字节边界对齐。RXDV保持有效,直到识别/T/R/分隔符、链路测试指示失败或SIGDET 变为假。

准备通过介质无关接口(MII模式)传输转换后的/J/K/的第一个半字节时,RXDV将置为有效。

#### 图3-3: 接收的数据与特定MII信号之间的关系

#### 3.1.2.8 接收器错误

在帧传输期间,意外的代码组会被视为接收错误。预期的代码组是数据集(0到F)和/T/R/(ESD)符号对。发生接收错误时,RXER信号置为有效并将任意数据驱动到RXD[1:0]线上。如果正在解码/J/K/分隔符期间检测到错误(不良SSD错误),则RXER将置为真并将值1110驱动到RXD[1:0]线上。请注意,不良SSD错误出现时,有效数据信号尚未置为有效。

#### 3.1.2.9 通过RMII接口传输的100M接收数据

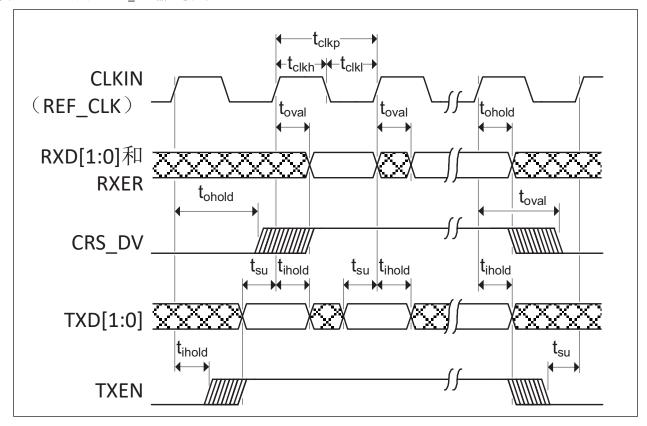

将2位数据半字节发送到RMII模块。这些数据半字节以50 MHz的速率随时钟输入控制器。控制器在XTAL1/CLKIN(REF\_CLK)的上升沿对数据进行采样。为确保满足建立和保持要求,半字节在XTAL1/CLKIN(REF\_CLK)的下降沿随时钟移出收发器。

#### 3.1.3 10BASE-T发送

要发送的数据来自MAC层控制器。10BASE-T发送器以2.5 MHz的速率从MII接收4位半字节,并将其转换为10 Mbps串行数据流。随后对数据流进行曼彻斯特编码并将其发送到模拟发送器,该发送器通过外部磁件将信号驱动到双绞线上。

10M发送器使用以下模块:

- MII (数字)

- TX 10M(数字)

- 10M发送器(模拟)

- 10M PLL (模拟)

#### 3.1.3.1 通过RMII接口传输的10M发送数据

MAC控制器将发送数据驱动到TXD总线上。TXD[1:0]应相对于REF\_CLK同步转换。当TXEN置为有效时,器件将接受TXD[1:0]以进行发送。当TXEN置为无效时,TXD[1:0]应为00以指示空闲,其他值均保留用于带外信号(待定义),器件应予以忽略。当TXEN置为有效时,TXD[1:0]应在每个REF\_CLK周期提供有效数据。

为了兼容传统的10BASE-T MAC/控制器,在半双工模式下,收发器会在接收路径上环回发送的数据。这并不会对MAC/控制器造成混淆,因为在此期间COL信号未置为有效。收发器还支持SQE(心跳)信号。

#### 3.1.3.2 曼彻斯特编码

将4位宽的数据发送到10M TX模块。半字节将转换为10 Mbps串行NRZI数据流。10M PLL锁定到外部时钟或内部振荡器并生成20 MHz时钟。这用于对NRZ数据流进行曼彻斯特编码。在没有发送任何数据(TXEN为低电平)时,10M TX模块输出正常链路脉冲(Normal Link Pulse,NLP)以与远程链路伙伴之间保持通信。

#### 3.1.3.3 10M发送驱动器

将曼彻斯特编码数据发送到模拟发送器,在此进行整形和滤波,之后作为差分信号在TXP和TXN输出端驱动输出。

### 3.1.4 10BASE-T接收

10BASE-T接收器通过磁件从线缆获取曼彻斯特编码模拟信号。该接收器会从信号中恢复接收时钟,并使用该时钟来恢复NRZI数据流。该10M串行数据将转换为4位数据半字节,随后以2.5 MHz的速率通过MII传递到控制器。该10M接收器使用以下模块:

- 滤波器和SQUELCH(模拟)

- 10M PLL(模拟)

- RX 10M(数字)

- MII (数字)

#### 3.1.4.1 10M接收输入和静噪

来自线缆的曼彻斯特信号通过1:1比例磁件馈入收发器(在输入RXP和RXN上)。该信号首先经过滤波以减少带外噪声。随后通过SQUELCH电路传递。SQUELCH是一组幅值和时序比较器,通常会抑制300 mV以下的差分电压,并检测和识别585 mV以上的差分电压。

#### 3.1.4.2 曼彻斯特解码

SQUELCH的输出进入10M RX模块,并在此验证是否为曼彻斯特编码数据。此外,还将检查信号的极性。如果极性相反(即,本地RXP与远程伙伴的RXN相连,或者本地RXN与远程伙伴的RXP相连),则会识别到并予以纠正。极性相反的情况由特殊控制/状态指示寄存器的XPOL位指示。10M PLL锁定到接收的曼彻斯特信号,由此生成20 MHz时钟。该时钟用于提取曼彻斯特编码数据并转换为10 MHz NRZI数据流。随后将其从串行数据转换为4位宽的并行数据。

10M RX模块还将检测有效的10Base-T空闲信号(正常链路脉冲(NLP))以保持链路。

#### 3.1.4.3 通过RMII接口传输的10M接收数据

将2位数据半字节发送到RMII模块。这些数据半字节在RMII REF\_CLK的上升沿有效。

#### 3.1.4.4 Jabber检测

Jabber是一种状态,在该状态下站执行发送操作的时间长于允许的最大数据包长度(通常因故障状态所致),这将导致在一段较长的时间内保持TXEN输入。器件将使用特殊逻辑来检测Jabber状态并在45 ms内中止向线路的发送。TXEN置为无效后,该逻辑将复位Jabber状态。

如第4.2.2节"基本状态寄存器"(第42页)所示,Jabber检测位表示检测到Jabber状态。

# 3.2 自动协商

自动协商功能的用途是根据其链路伙伴的能力将收发器自动配置为最优链路参数。自动协商是一种在两个链路伙伴之间交换配置信息和自动选择双方支持的最高性能工作模式的机制。自动协商在IEEE 802.3规范的第28条中有完整定义。

自动协商完成后,有关已解析链路的信息将通过串行管理接口(SMI)传递回控制器。协商过程的结果反映在 PHY特殊控制/状态寄存器的速度指示和自动协商通告寄存器中。自动协商协议纯粹是物理层活动,其执行与MAC 控制器无关。

收发器通告的能力存储在自动协商通告寄存器中。收发器通告的默认能力取决于用户定义的片上信号选项。 自动协商会话期间将激活以下模块:

- 自动协商(数字)

- 100M ADC (模拟)

- 100M PLL (模拟)

- 100M均衡器/BLW/时钟恢复(DSP)

- 10M SQUELCH(模拟)

- 10M PLL (模拟)

- 10M发送器(模拟)

使能时,发生以下任何事件均会启动自动协商:

- 硬件复位

- 软件复位

- 掉电复位

- 链路状态中断

- 将基本控制寄存器的重启自动协商位置1

检测到其中一个事件时,收发器通过发送快速链路脉冲(Fast Link Pulse,FLP)突发启动自动协商,链路脉冲突发来自10M发送器。这些脉冲被整形为正常链路脉冲,并且可以无损地传递至CAT-3或CAT-5线缆。一个快速链路脉冲突发包含最多33个脉冲。始终存在的17个奇数脉冲构成FLP突发。可能存在或缺失的16个偶数脉冲包含正在发送的数据字。存在数据脉冲用1表示,缺失用0表示。

FLP突发发送的数据称为"链路代码字"。它们在IEEE 802.3第28条中有完整定义。总的来说,收发器在其选择器位域(链路代码字的前5位)中通告802.3的合规性。它根据自动协商通告寄存器中设置的位通告其技术能力。

存在4种可能的技术能力匹配。按优先级依次为:

- 100M全双工(最高优先级)

- 100M半双工

- 10M全双工

- 10M半双工(最低优先级)

如果通告收发器具有完全能力(100M,全双工)且链路伙伴支持10M和100M,则自动协商将选择100M作为最高性能模式。如果链路伙伴支持半双工和全双工模式,则自动协商将选择全双工作为最高性能模式。

确定能力匹配后,将重复发送链路代码字(应答位置1)。此时,链路代码字的主要内容中如果存在任何差异,都将导致自动协商重启。如果未接收到所需的全部FLP突发,则自动协商也将重启。

收发器在自动协商期间通告的能力最初取决于复位完成后锁存在MODE[2:0]配置脚上的逻辑电平。这些配置脚也可用于禁止在上电时自动协商。更多信息,请参见第3.7.2节"MODE[2:0]:模式配置"(第27页)。

通过写入自动协商通告寄存器的bit[8:5],就可以使用软件来控制收发器通告的能力。写入自动协商通告寄存器不会自动重启自动协商。通告新能力之前,必须将基本控制寄存器的重启自动协商位置1。也可以通过软件将基本控制寄存器的自动协商使能位清零来禁止自动协商。

注: 该器件不支持"下一页"功能。

## 3.2.1 并行检测

如果与CN8020相连的器件不能自动协商(例如,未检测到FLP),则可以根据100M MLT-3符号或10M正常链路脉冲确定链路速度。这种情况下,将根据IEEE标准假定链路为半双工。这种能力称为"并行检测"。该特性可确保与传统链路伙伴的互操作性。如果通过并行检测构成链路,则将自动协商通告寄存器的链路伙伴自动协商功能位清零以指示链路伙伴不能自动协商。控制器可以通过管理接口访问该信息。如果并行检测期间发生故障,则链路伙伴自动协商功能的并行检测故障位置1。

自动协商通告寄存器用于存储链路伙伴能力信息,该信息编码在接收的FLP中。如果链路伙伴不能自动协商,则 在完成并行检测后更新自动协商通告寄存器以反映链路伙伴的速度能力。

### 3.2.2 重启自动协商

可以随时通过将基本控制寄存器的重启自动协商位置1来重启自动协商。链路断开时,自动协商也将随时重启。 链路断开是由于信号损耗所致。发生这种情况的原因可能是由于线缆断开或链路伙伴发送的信号中断。尝试恢复 自动协商以确定新的链路配置。

如果管理实体通过将基本控制寄存器的重启自动协商位置1重启自动协商,则CN8020将停止所有发送/接收操作,以此作为响应。在自动协商状态机中完成break\_link\_timer(约1200 ms)后,自动协商将重启。在这种情况下,链路伙伴会由于缺少接收信号而断开链路,因此也会重新开始自动协商。

#### 3.2.3 禁止自动协商

可以通过将基本控制寄存器的自动协商使能位清零来禁止自动协商。之后,器件将强制其运行速度以反映基本控制寄存器(速度选择位和双工模式位)中的信息。使能自动协商时,这些位应被忽略。

#### 3.2.4 半双工与全双工

半双工运行依赖于载波侦听多路访问/冲突检测(Carrier Sense Multiple Access/Collision Detect,CSMA/CD)协议来处理网络通信和冲突。在该模式下,载波侦听信号CRS响应发送和接收活动。如果在收发器发送数据期间接收数据,则会发生冲突。

在全双工模式下,收发器能够同时发送和接收数据。在该模式下,CRS仅响应接收活动。CSMA/CD协议不适用,并且会禁止冲突检测。

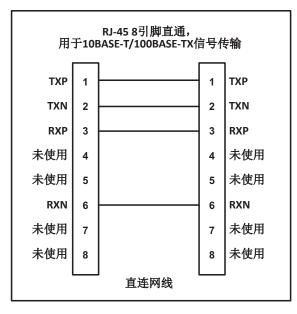

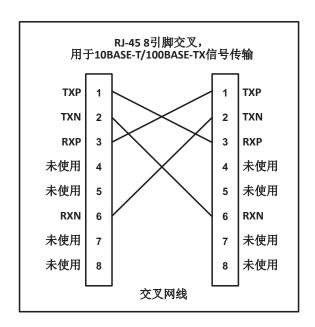

# 3.3 支持HP自动MDIX

借助HP自动MDIX,可以方便地使用CAT-3(10BASE-T)或CAT-5(100BASE-T)介质UTP互连线缆,无需考虑接口接线方案。如果用户插入直连或交叉网线(如图3-4所示),则器件的自动MDIX收发器能够配置TXP/TXN和RXP/RXN引脚以确保正常运行。

器件的内部逻辑会检测连接器件的TX和RX引脚。由于RX和TX线对可以互换,因此需要遵守特殊的PCB设计注意事项以适应自动MDIX设计的对称磁件和端接。

自动MDIX功能可通过特殊控制/状态指示寄存器的AMDIXCTRL位禁止。

图3-4: 直连网线与交叉网线

# 3.4 MAC接口

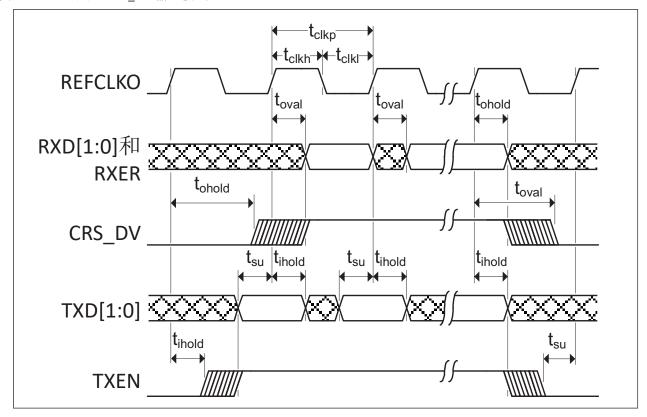

### 3.4.1 RMII

该器件支持在以太网收发器和开关ASIC之间使用的低引脚数精简介质无关接口(Reduced Media Independent Interface,RMII)。根据IEEE 802.3定义,MII由16个数据和控制引脚组成。在集成了多个MAC或收发器接口(例如开关)的器件中,引脚数会随着端口数的增加而增加,进而导致成本大幅增加。RMII减少了该引脚数,同时保留了与MII相同的管理接口(MDIO/MDC)。

#### RMII接口具有以下特性:

- 能够支持10 Mbps和100 Mbps数据速率

- 发送和接收使用同一个时钟参考

- 提供独立的2位(双位)宽发送和接收数据路径

- 使用LVCMOS信号电平,与常见的数字CMOS ASIC工艺兼容

RMII包括以下接口信号(1个可选):

- 发送数据——TXD[1:0]

- 发送选通——TXEN

- 接收数据——RXD[1:0]

- 接收错误——RXER(可选)

- 载波侦听——CRS DV

- 参考时钟——(RMII参考通常将该信号定义为REF\_CLK)

#### 3.4.1.1 CRS\_DV——载波侦听/接收数据有效

当接收介质处于非空闲状态时,器件会将CRS\_DV置为有效。根据工作模式相关标准,在检测到载波时,CRS\_DV将以异步方式置为有效。当在10BASE-T模式下通过静噪时,或者在100BASE-X模式下检测到10位中有2个不连续的零时,将认为检测到载波。

载波丢失会导致与RXD[1:0]上显示半字节第一个双位的REF\_CLK周期同步的CRS\_DV置为无效(例如,CRS\_DV仅在半字节边界置为无效)。首次将CRS\_DV置为无效后,如果器件还有其他位要显示在RXD[1:0]上,则器件应在显示每个半字节的第二个双位的REF\_CLK周期将CRS\_DV置为有效,并在显示半字节的第一个双位的REF\_CLK周期将CRS\_DV置为无效。其结果是,从半字节边界开始,当CRS在RXDV之前结束(例如,当载波事件结束时FIFO仍有要发送的位)时,CRS\_DV以25 MHz(100 Mbps模式下)或2.5 MHz(10 Mbps模式下)的频率翻转。因此,MAC能够精确地恢复RXDV和CRS。

在假载波事件期间,CRS\_DV应在载波活动过程中保持有效。在CRS\_DV置为有效后,RXD[1:0]上的数据即视为有效。不过,由于CRS\_DV相对于REF\_CLK以异步方式置为有效,所以在正确解码接收信号之前,RXD[1:0]上的数据应一直为00。

#### 3.4.1.2 参考时钟(REF CLK)

RMII REF\_CLK是一个连续的时钟,用于为CRS\_DV、RXD[1:0]、TXEN、TXD[1:0]和RXER提供时序参考。器件将REF\_CLK用作网络时钟,因此在发送数据路径上无需缓冲。但是,在接收数据路径上,接收器会从传入的数据流中恢复时钟,而器件会通过弹性缓冲来适应恢复的时钟与本地REF CLK之间的差异。

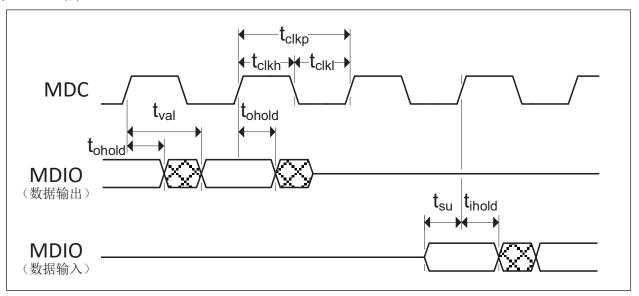

### 3.5 串行管理接口(SMI)

串行管理接口用于控制器件和获取器件状态。该接口支持802.3标准第22条要求的寄存器0到6,以及该规范允许的"供应商特定"寄存器16到31。不支持的寄存器(例如7到15)将读为十六进制数"FFFF"。有关器件寄存器的详细信息,请参见第4.0章"寄存器说明"(第40页)。

在系统层面上,SMI提供2个信号: MDIO和MDC。MDC信号是站管理控制器(Station Management Controller,SMC)提供的非周期性时钟。MDIO是双向数据SMI输入/输出信号,它从控制器SMC接收串行数据(命令),并向SMC发送串行数据(状态)。MDC各边沿之间的最短时间为160 ns,没有最长时间。最短周期时间(两个连续上升沿或两个连续下降沿之间的时间)为400 ns。遵守这些适度的时序要求能够使单片机的I/O端口轻松驱动该接口。

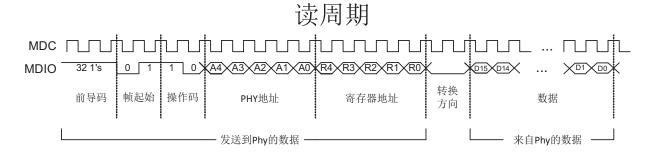

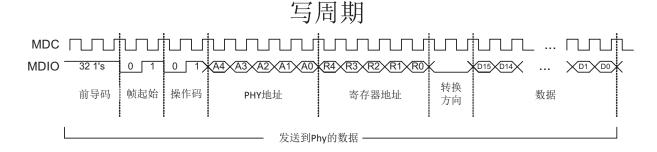

MDIO线路上的数据在MDC的上升沿锁存。数据的帧结构和时序如图3-5和图3-6所示。第5.6.5节"SMI时序"(第60页)将对MDIO信号的时序关系进行进一步说明。

图3-5: MDIO时序和帧结构——读周期

图3-6: MDIO时序和帧结构——写周期

# 3.6 中断管理

器件管理接口支持IEEE 802.3规范之外的中断功能。只要检测到通过中断屏蔽寄存器设置的特定事件,该中断功能就会在nINT输出上产生一个低电平有效的异步中断信号。

器件的中断系统提供两种模式:主要中断模式和备用中断模式。当相应的屏蔽位置1时,两个系统都会将nINT引脚置为低电平。这些模式之间的差别仅在于将nINT中断输出置为无效的方式。以下几小节对这些模式进行了详细介绍。

注: 上电或硬复位后的默认中断模式为主要中断模式,而备用中断模式需要设置。

### 3.6.1 主要中断系统

主要中断系统为默认中断模式(模式控制/状态寄存器的ALTINT位为0)。上电或硬复位后,始终选择主要中断系统。在该模式下,要设置中断,应将中断屏蔽寄存器中的相应屏蔽位置1(见表3-2)。之后,当将nINT置为有效的事件为真时,nINT输出将被置为有效。当将nINT置为无效的事件为真时,nINT将被置为无效。

表3-2: 中断管理表

| 掩码   | 中断源标志 |               | 中断源标志中断源 |          | 将nINT置为有效的<br>事件                   | 将nINT置为无效的事件                            |

|------|-------|---------------|----------|----------|------------------------------------|-----------------------------------------|

| 30.7 | 29.7  | ENERGYON      | 17.1     | ENERGYON | <b>17.1</b> 上升沿<br>( <b>注3-1</b> ) | 17.1下降沿或读寄存器29                          |

| 30.6 | 29.6  | 自动协商完成        | 1.5      | 自动协商完成   | 1.5上升沿                             | 1.5下降沿或读寄存器29                           |

| 30.5 | 29.5  | 检测到远程故障       | 1.4      | 远程故障     | 1.4上升沿                             | 1.4下降沿、读寄存器1或<br>读寄存器29                 |

| 30.4 | 29.4  | 链路断开          | 1.2      | 链路状态     | 1.2下降沿                             | 读寄存器1或读寄存器29                            |

| 30.3 | 29.3  | 自动协商LP应答      | 5.14     | 应答       | 5.14上升沿                            | 5.14下降沿或读寄存器29                          |

| 30.2 | 29.2  | 并行检测故障        | 6.4      | 并行检测故障   | 6.4上升沿                             | 6.4下降沿、读寄存器6、读寄存器29、重新自动协商或链接断开         |

| 30.1 | 29.1  | 接收到自动协商<br>页面 | 6.1      | 页接收      | 6.1上升沿                             | 6.1下降沿、读寄存器6、<br>读寄存器29、重新自动协<br>商或链接断开 |

**注3-1** 如果在ENERGYON仍为高电平时使能了屏蔽位并已将nINT置为无效,则在拔下线缆时ENERGYON变为低电平后一秒钟左右,nINT将置为有效并持续256 ms。为防止意外将nINT置为有效,作为ENERGYON中断服务程序的一部分,应始终将ENERGYON中断屏蔽位清零。

注: 在信号采集过程开始时,模式控制/状态寄存器中的ENERGYON位默认置为1,因此中断屏蔽寄存器中的INT7位在上电时也将读为1。如果没有信号,则ENERGYON和INT7将在几毫秒内清零。

### 3.6.2 备用中断系统

备用中断系统可通过将模式控制/状态寄存器的ALTINT位置1来使能。在该模式下,要设置中断,应将屏蔽寄存器30中的相应位置1(见表3-3。要清除中断,可以清零中断屏蔽寄存器中的相应位以将nINT输出置为无效,或者清除中断源并向相应的中断源标志写1。向中断源标志写1将使状态机检查中断源,以此确定中断源标志是应清零还是保持为1。如果置为无效的条件为真,则中断源标志清零,nINT也将置为无效。如果置为无效的条件为假,则中断源标志保持置1,nINT也保持有效。

例如,将中断屏蔽寄存器中的INT7位置1将允许ENERGYON中断。插入线缆后,模式控制/状态寄存器中的ENERGYON位变为有效,nINT将置为低电平。要将nINT中断输出置为无效,可以通过移除线缆并向中断屏蔽寄存器中的INT7位写1来清零模式控制/状态寄存器中的ENERGYON位,或者清零INT7屏蔽(中断屏蔽寄存器的bit 7)。

表3-3: 备用中断系统管理表

| 掩码   |      | 中断源标志         |      | 中断源      | 将nINT置为<br>有效的事件 | 置为无效的<br>条件 | 清除nINT的位 |

|------|------|---------------|------|----------|------------------|-------------|----------|

| 30.7 | 29.7 | ENERGYON      | 17.1 | ENERGYON | 17.1上升沿          | 17.1低电平     | 29.7     |

| 30.6 | 29.6 | 自动协商完成        | 1.5  | 自动协商完成   | 1.5上升沿           | 1.5低电平      | 29.6     |

| 30.5 | 29.5 | 检测到远程故障       | 1.4  | 远程故障     | 1.4上升沿           | 1.4低电平      | 29.5     |

| 30.4 | 29.4 | 链路断开          | 1.2  | 链路状态     | 1.2下降沿           | 1.2高电平      | 29.4     |

| 30.3 | 29.3 | 自动协商LP应答      | 5.14 | 应答       | 5.14上升沿          | 5.14低电平     | 29.3     |

| 30.2 | 29.2 | 并行检测故障        | 6.4  | 并行检测故障   | 6.4上升沿           | 6.4低电平      | 29.2     |

| 30.1 | 29.1 | 接收到自动协商<br>页面 | 6.1  | 页接收      | 6.1上升沿           | 6.1低电平      | 29.1     |

注: 在信号采集过程开始时,模式控制/状态寄存器中的ENERGYON位默认置为1,因此中断屏蔽寄存器中的INT7位在上电时也将读为1。如果没有信号,则ENERGYON和INT7将在几毫秒内清零。

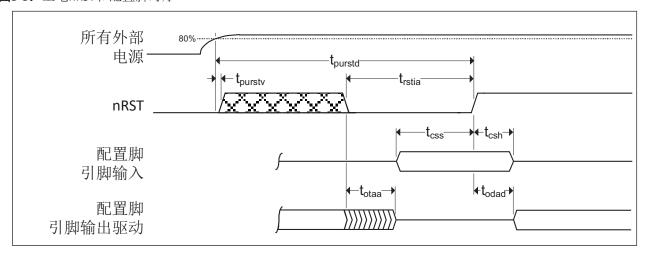

## 3.7 配置脚

通过配置脚,可将器件的各种功能自动配置为用户定义的值。配置脚在上电复位(Power-On Reset,POR)和引脚复位(nRST)时锁存。配置脚具有内部电阻,用于防止信号在未连接时悬空。如果特定配置脚与负载相连,则应使用外部上拉或下拉电阻来增大内部电阻,以确保内部电阻在锁存前达到所需电压。也可通过添加外部电阻来改变内部电阻。

- **注3-2** 系统设计人员必须保证配置脚引脚符合第5.6.3节"上电nRST和配置脚时序"(第56页)中指定的时序要求。如果配置脚引脚锁存之前未处于正确的电压值,则器件可能会捕捉到不正确的配置脚值。

- **注3-3** 当从外部将配置脚拉高时,应将配置脚连接到VDDIO,但<u>REGOFF</u>和<u>nINTSEL</u>除外,它们应连接到VDD2A。

#### 3.7.1 PHYAD[0]: PHY地址配置

PHYADO位被驱动为高电平或低电平,以便为每个PHY提供惟一的地址。该地址在硬件复位结束时锁存到内部寄存器中(默认值 = 0b)。在多PHY应用(例如中继器)中,控制器可以通过惟一的地址对每个PHY进行管理。每个PHY都会检查各管理数据帧内相关位中的地址是否匹配。识别到匹配后,PHY会响应该特定帧。PHY地址还用于产生加扰器种子。在多PHY应用中,这可确保加扰器不同步,并在整个频谱上分散电磁辐射。

可以使用硬件配置将器件的SMI地址配置为值0或1。如果需要大于1的地址,则用户可以使用软件配置来配置PHY地址。可以使用特殊模式寄存器的PHYAD位写入PHY地址(在某一地址建立SMI通信后)。PHYADO硬件配置脚与RXER引脚复用。

# 3.7.2 <u>MODE[2:0]</u>: 模式配置

MODE[2:0]配置脚控制10/100数字模块的配置。当nRST引脚置为无效时,将根据MODE[2:0]配置脚载入寄存器位值。随后由寄存器位值配置10/100数字模块。通过基本控制寄存器的软复位位触发软复位时,10/100数字模块的配置由寄存器位值控制,而MODE[2:0]配置脚不起作用。

器件的模式可以使用表3-4总结的硬件配置脚进行配置。用户可以通过写入SMI寄存器来配置收发器模式。

表3-4: MODE[2:0]总线

|           |                                                                                                                         | 默认寄存                 | 字器位值      |

|-----------|-------------------------------------------------------------------------------------------------------------------------|----------------------|-----------|

| MODE[2:0] | 模式定义                                                                                                                    | 寄存器0                 | 寄存器4      |

|           |                                                                                                                         | [13,12,10,8]         | [8,7,6,5] |

| 000       | 10Base-T半双工。禁止自动协商。                                                                                                     | 0000                 | N/A       |

| 001       | 10Base-T全双工。禁止自动协商。                                                                                                     | 0001                 | N/A       |

| 010       | 100Base-TX半双工。禁止自动协商。<br>发送和接收期间CRS处于有效状态。                                                                              | 1000                 | N/A       |

| 011       | 100Base-TX全双工。禁止自动协商。接收期间CRS<br>处于有效状态。                                                                                 | 1001                 | N/A       |

| 100       | 通告100Base-TX半双工。使能自动协商。<br>发送和接收期间CRS处于有效状态。                                                                            | 1100                 | 0100      |

| 101       | 中继器模式。使能自动协商。通告100Base-TX半双工。<br>接收期间CRS处于有效状态。                                                                         | 1100                 | 0100      |

| 110       | 掉电模式。在该模式下,收发器将在掉电模式下唤醒。当MODE[2:0]位设置为该模式时,不能使用收发器。要退出该模式,必须将寄存器18.7:5中的MODE位(见第4.2.9节"特殊模式寄存器"(第47页))配置为其他值,并且必须发出软复位。 | N/A                  | N/A       |

| 111       | 具备完全能力。使能自动协商。                                                                                                          | <b>X</b> 10 <b>X</b> | 1111      |

MODE[2:0]硬件配置引脚与其他信号复用,如表3-5所示。

表3-5: 模式位的引脚名称

| 模式位     | 引脚名称                 |

|---------|----------------------|

| MODE[0] | RXD0/ <u>MODE0</u>   |

| MODE[1] | RXD1/ <u>MODE1</u>   |

| MODE[2] | CRS_DV/ <u>MODE2</u> |

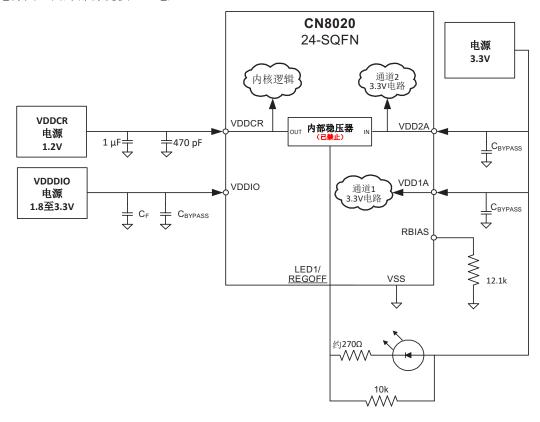

### 3.7.3 REGOFF: 内部+1.2V稳压器配置

通过集成flexPWR技术禁止内部+1.2V稳压器。禁止稳压器时,必须向VDDCR引脚提供一个外部+1.2V电压。禁止内部+1.2V稳压器可以降低系统总功耗,因为可以使用效率更高的外部开关稳压器(相对于内部线性稳压器)为收发器电路提供+1.2V电压。

**注:** 由于<u>REGOFF</u>配置脚与LED1引脚功能复用,因此还必须适当地考虑LED的极性。有关<u>REGOFF</u>和LED1极性关系的更多信息,请参见第3.8.1.1节"REGOFF和LED1极性选择"(第31页)。

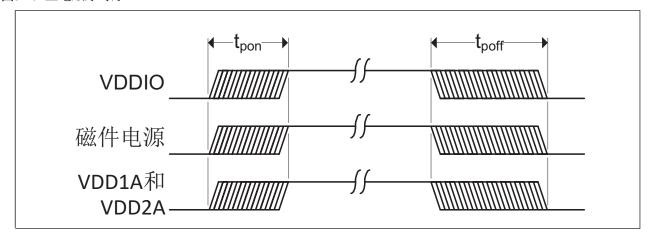

#### 3.7.3.1 禁止内部+1.2V稳压器

要禁止+1.2V内部稳压器,应在REGOFF配置脚与VDD2A之间连接一个上拉配置脚电阻。上电时,在VDDIO和VDD2A均符合规范后,收发器将对REGOFF进行采样以确定是否应开启内部稳压器。如果在该引脚上采样到高于V<sub>II</sub>的电压,则禁止内部稳压器,系统必须向VDDCR引脚提供+1.2V的电压。在将电压施加到VDDCR之前,VDDIO电压必须至少为工作电压的80%(1.8V工作电压时为1.44V,2.5V工作电压时为2.0V,3.3V工作电压时为2.64V)。如第3.7.3.2节所述,当REGOFF悬空或连接至VSS时,内部稳压器使能,系统无需向VDDCR引脚提供+1.2V的电压。

#### 3.7.3.2 使能内部+1.2V稳压器

除非使用<u>REGOFF</u>配置脚将收发器配置为稳压器关闭模式(如第3.7.3.1节所述),否则由片上稳压器向VDDCR提供+1.2V电压。默认情况下,内部+1.2V稳压器在<u>REGOFF</u>悬空时使能(因内部下拉电阻所致)。上电期间,如果在REGOFF上采样到低于V<sub>1</sub>的电压,则内部+1.2V稳压器将开启并在VDD2A引脚的供电下工作。

#### 3.7.4 nINTSEL: nINT/REFCLKO配置

<u>nINTSEL</u>配置脚用于选择两种可用模式之一: REF\_CLK输入模式(nINT)和REF\_CLK输出模式。配置的模式将决定 nINT/REFCLKO引脚的功能。<u>nINTSEL</u>配置脚在POR时以及nRST的上升沿锁存。默认情况下,<u>nINTSEL</u>通过内部上拉电阻配置为nINT模式。

表3-6: nINTSEL配置

| 配置脚值               | 模式          | REF_CLK说明                                                            |

|--------------------|-------------|----------------------------------------------------------------------|

| <u>nINTSEL</u> = 0 | REF_CLK输出模式 | nINT/REFCLKO是REF_CLK的时钟源。                                            |

| <u>nINTSEL</u> = 1 | REF_CLK输入模式 | nINT/REFCLKO是低电平有效的中断输出。<br>REF_CLK的时钟源来自外部,并且必须在XTAL1/CLKIN引脚上进行驱动。 |

RMII REF\_CLK是一个连续的时钟,用于为CRS\_DV、RXD[1:0]、TXEN、TXD[1:0]和RXER提供时序参考。器件将REF\_CLK用作网络时钟,因此在发送数据路径上无需缓冲。但是,在接收数据路径上,接收器从传入的数据流中恢复时钟。器件使用弹性缓冲来适应恢复的时钟与本地REF CLK之间的差异。

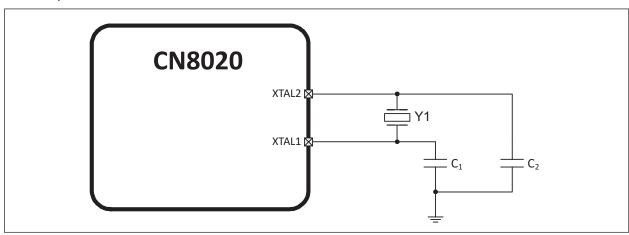

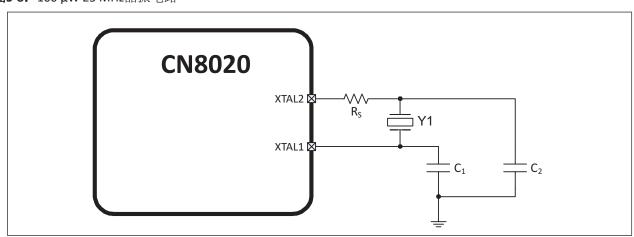

在REF\_CLK输入模式下,50 MHz REF\_CLK在XTAL1/CLKIN引脚上进行驱动。这是使用RMII时的传统系统配置,具体说明请参见第3.7.4.1节。当配置为REF\_CLK输出模式时,器件将产生50 MHz RMII REF\_CLK,并且nINT中断不可用。REF\_CLK输出模式允许将低成本的25 MHz晶振用作REF\_CLK参考。该配置可以降低系统成本,具体说明请参见第3.7.4.2节。

**注:** 由于<u>nINTSEL</u>配置脚与LED2引脚功能复用,因此还必须适当地考虑LED的极性。有关<u>nINTSEL</u>和LED2极性关系的更多信息,请参见第3.8.1.2节"nINTSEL和LED2极性选择"(第31页)。

#### 3.7.4.1 REF CLK输入模式

在REF\_CLK输入模式下,50 MHz REF\_CLK在XTAL1/CLKIN引脚上进行驱动。使用该模式时,必须在器件外部为REF\_CLK提供50 MHz时钟源。该时钟被驱动到MAC和PHY,如图3-7所示。

图3-7: 为REF CLK提供外部50 MHz时钟源

### 3.7.4.2 REF\_CLK输出模式

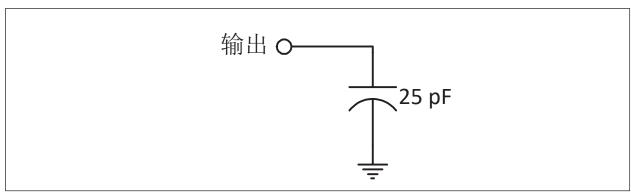

为降低BOM成本,该器件配备通过低成本25 MHz基频晶振来生成RMII REF\_CLK信号的功能。与通常需要50 MHz的 3次谐波晶振相比,这类晶振价格更低廉。MAC必须支持外部时钟才能使用该功能,如图3-8所示。

为优化封装尺寸和成本,REFCLKO引脚与nINT引脚复用。在REF\_CLK输出模式下,会禁止nINT功能以适应将REFCLKO用作MAC的50 MHz时钟。

**注:** REF\_CLK输出模式不属于RMII规范的一部分。该模式下的时序不符合RMII规范。为确保系统正常工作,必须对MAC和CN8020执行时序分析。

图3-8: 通过25 MHz晶振生成REF\_CLK

注: nINT在该配置中不可用

在一些系统架构中,可以使用25 MHz时钟源。该器件可用于生成MAC的REF\_CLK,如图3-9所示。需要注意的是,在该特定示例中,只能使用25 MHz时钟(时钟不得为50 MHz)。与25 MHz晶振模式相似,nINT功能被禁止。

**图3-9:** 通过外部25 MHz时钟源生成REF\_CLK

注: nINT在该配置中不可用

# 3.8 其他功能

#### 3.8.1 LED

器件提供两个LED信号,以便确定收发器的工作模式。所有LED信号均为高电平有效或低电平有效,如第3.8.1.2节 "nINTSEL和LED2极性选择"(第31页)和第3.8.1.2节 "nINTSEL和LED2极性选择"(第31页)所述。

只要器件检测到有效链路,LED1输出就将驱动为有效状态,并在CRS处于有效状态(高电平)时闪烁以指示活动。 当工作速度为100 Mbps时,LED2输出将驱动为有效状态。当工作速度为10 Mbps时,或者线路隔离期间,该LED 将熄灭。

注: 在将LED1和LED2引脚拉高时,必须将它们连接至VDD2A,而不是VDDIO。

#### 3.8.1.1 REGOFF和LED1极性选择

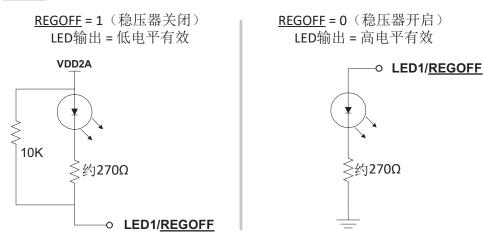

REGOFF配置脚与LED1引脚复用。LED1输出将根据是否存在外部上拉电阻来自动更改极性。如果通过外部上拉电阻将LED1引脚拉高至VDD2A,以此为REGOFF选择逻辑高电平,则LED1输出将为低电平有效。如果通过内部下拉电阻将LED1引脚拉低,以此为REGOFF选择逻辑低电平,则LED1输出将为高电平有效。图3-10详细说明了每个REGOFF配置的LED1极性。

图3-10: LED1/REGOFF极性配置

注: 有关REGOFF配置脚的更多信息,请参见第3.7.3节"REGOFF:内部+1.2V稳压器配置"(第28页)。

### 3.8.1.2 nINTSEL和LED2极性选择

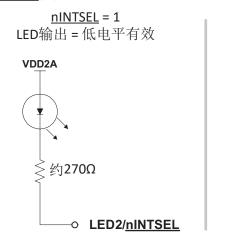

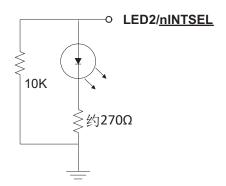

<u>nINTSEL</u>配置脚与LED2引脚复用。LED2输出将根据是否存在外部下拉电阻来自动更改极性。如果将LED2引脚拉高至VDD2A,以此为<u>nINTSEL</u>选择逻辑高电平,则LED2输出将为低电平有效。如果通过外部下拉电阻将LED2引脚拉低,以此为<u>nINTSEL</u>选择逻辑低电平,则LED2输出将为高电平有效输出。图3-11详细说明了每个<u>nINTSEL</u>配置的LED2极性。

图3-11: LED2/nINTSEL极性配置

**注:** 有关nINTSEL配置脚的更多信息,请参见第3.7.4节 "nINTSEL: nINT/REFCLKO配置"(第28页)。

### 3.8.2 可变电压I/O

该器件的数字I/O引脚具有可变电压,使其能够利用缩减技术带来的低功耗优势。这些引脚可以在+1.62V至+3.6V的低I/O电压范围内工作。施加的I/O电压值必须保持在±10%的容差范围内。在收发器完成上电复位后,升高或降低电压都会导致收发器操作出错。更多信息,请参见第5.0章"工作特性"(第50页)。

注: 对器件上电之前,不得将输入信号驱动为高电平。

### 3.8.3 掉电模式

器件有两种掉电模式:常规掉电模式和电能检测掉电模式。以下几小节对这两种模式进行了详细介绍。

#### 3.8.3.1 常规掉电

该掉电模式通过基本控制寄存器的掉电位控制。在该模式下,只要掉电位为1,整个收发器(管理接口除外)就将掉电并保持该模式。当掉电位清零时,收发器上电并自动复位。

#### 3.8.3.2 电能检测掉电

该掉电模式通过将模式控制/状态寄存器的EDPWRDOWN位置1来激活。在该模式下,当线路上没有电能时,收发器将掉电(管理接口、SQUELCH电路和ENERGYON逻辑除外)。ENERGYON逻辑用于检测100BASE-TX、10BASE-T或自动协商信号是否存在有效电能。

在该模式下,当模式控制/状态寄存器的ENERGYON位为低电平时,收发器将掉电,并且不发送任何数据。当通过链路脉冲或数据包接收到电能时,ENERGYON位变为高电平,收发器上电。如果在中断屏蔽寄存器中允许了ENERGYON中断,则器件将自动复位到掉电之前的状态,并将nINT中断置为有效。用于激活ENERGYON的第一个(也可能是第二个)数据包可能会丢失。

当模式控制/状态寄存器的EDPWRDOWN位为低电平时,禁止电能检测掉电。

#### 3.8.4 隔离模式

通过将基本控制寄存器的隔离位置1,可以将器件数据路径与RMII接口电气隔离。在隔离模式下,收发器不响应TXD、TXEN和TXER输入,但会响应管理事务。

通过隔离,可以让多个收发器连接到同一RMII接口且不发生争用。默认情况下,收发器不隔离(上电时(隔离 = 0))。

### 3.8.5 复位

器件提供两种复位形式:硬件复位和软件复位。硬件复位和软件复位均会复位器件寄存器。选择寄存器位(在寄存器定义中由"NASR"指示)不会被软件复位清零。第3.8.3节中介绍的掉电模式不会复位寄存器。

**注:** 退出复位后的前16 μs,RMII接口将以2.5 MHz运行。此段时间过后,如果使能了自动协商,则将切换至 25 MHz。

#### 3.8.5.1 硬件复位

通过将nRST输入引脚驱动为低电平,可以将硬件复位置为有效。驱动时,nRST保持低电平的时间应达到第5.6.3节"上电nRST和配置脚时序"(第56页)所述的最短时间,以确保收发器正确复位。硬件复位期间,**必须**向 XTAL1/CLKIN信号提供外部时钟。

**注:** 上电后需要进行硬件复位(nRST置为有效)。更多信息,请参见第5.6.3节"上电nRST和配置脚时序"(第56页)。

#### 3.8.5.2 软件复位

通过将基本控制寄存器的软复位位置1,可以激活软件复位。除了在寄存器定义中由"NASR"指示的位之外,所有寄存器位均会被软件复位清零。软复位位自行清零。根据IEEE 802.3u标准第22条(22.2.4.1.1),复位过程将在该位置1后的0.5s内完成。

#### 3.8.6 载波侦听

载波侦听(CRS)从CRS\_DV引脚输出。CRS是由IEEE 802.3u标准中的MII规范定义的信号。当收发器处于中继器模式或全双工模式时,器件仅根据接收活动将CRS置为有效。其他情况下,收发器根据发送或接收活动将CRS置为有效。

载波侦听逻辑使用未加扰的编码数据来确定载波活动状态。在检测到任意10位中有2个不连续的零时,该逻辑将激活载波侦听。如果在/J/K/流起始分隔符对之前检测到10个连续的1,则载波侦听终止。如果检测到SSD对,则载波侦听置为有效,直到检测到/T/R/流结束分隔符对或一对空闲符号为止。在/T/符号或第一个空闲符号之后,载波置为无效。如果/T/后未跟随/R/,则载波保持有效。对于后跟一些非空闲符号的空闲符号,载波的处理方式与之类似。

### 3.8.7 链路完整性测试

器件按照IEEE 802.3u(第24-15条)链路监视状态图中所述执行链路完整性测试。链路状态与10 Mbps链路状态复用,以构成基本控制寄存器的链路状态位并驱动LINK LED(LED1)。

DSP使用内部的DATA\_VALID信号向链路监视状态机指示RXP和RXN信号中存在有效的MLT-3波形(根据ANSI X3.263 TP-PMD标准的定义)。当DATA\_VALID置为有效时,控制逻辑进入链路就绪状态,并等待自动协商模块的使能信号。接收到使能信号后,将进入链路接通状态,发送和接收逻辑模块变为有效。如果禁止自动协商,则链路完整性逻辑将在DATA VALID置为有效时立即进入链路接通状态。

为了使线路稳定下来,链路完整性逻辑将从DATA\_VALID置为有效时开始至少等待330 μs,直到进入链路就绪状态为止。只要将DATA\_VALID输入置为无效,该逻辑就会立即使链路信号无效并进入链路断开状态。 当10/100数字模块处于10BASE-T模式时,链接状态将来自10BASE-T接收器逻辑。

### 3.8.8 环回工作模式

器件可以配置为近端环回和远端环回。以下几小节对这两种环回模式进行了详细介绍。

#### 3.8.8.1 近端环回

近端环回模式会将数字发回接收端以进行测试,如图3-12蓝色箭头所示。近端环回模式通过将基本控制寄存器的环回位置1来使能。在近端环回模式下,大部分数字电路都保持工作状态,因为数据在环回之前会经由PCS和PMA层传输到PMD子层。无论TXEN信号的状态如何,发送器都掉电。

#### 图3-12: 近端环回框图

####

远端环回是MDI(模拟)环回的一种特殊测试模式,如图3-14中的蓝色箭头所示。远端环回模式通过将模式控制/状态寄存器的FARLOOPBACK位置1来使能。在该模式下,从MDI上的链路伙伴接收到的数据将环回到链路伙伴。本地MAC接口上的数字接口信号被隔离。

图3-13: 远端环回框图

### 3.8.8.3 连接器环回

器件在非常短的线缆上保持可靠传输,并且可在连接器环回中进行测试,如图3-14所示。RJ45环回线缆可用于将来自变压器输出的发送信号传输回接收器输入,该环回能够以10 Mbps和100 Mbps的速率工作。

图3-14: 连接器环回框图

RJ45环回线缆。通过连接引脚1与引脚3以及连接引脚2与引脚6来构建。

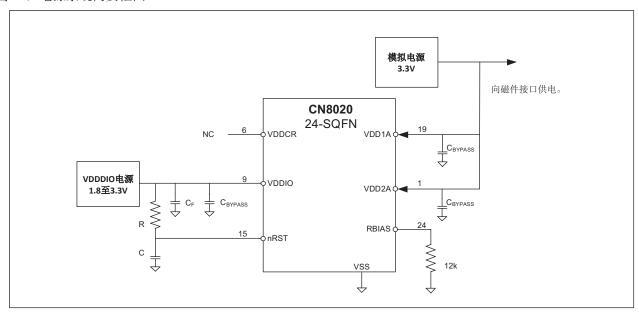

# 3.9 应用图

本节提供了以下方面的典型应用图:

- 简化的系统级应用图

- 电源图(由内部稳压器提供1.2V电压)

- 电源图(由外部源提供1.2V电压)

- 双绞线接口图(单电源)

- 双绞线接口图(双电源)

# 3.9.1 简化的系统级应用图

图3-15: 简化的系统级应用图

### 3.9.2 电源图(由内部稳压器提供1.2V电压)

图3-16: 电源图(由内部稳压器提供1.2V电压)

### 3.9.3 电源图(由外部源提供1.2V电压)

图3-17: 电源图(由外部源提供1.2V电压)

#### 3.9.4 双绞线接口图(单电源)

图3-18: 双绞线接口图(单电源)

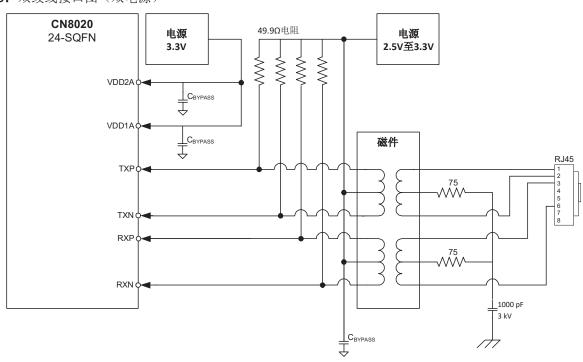

### 3.9.5 双绞线接口图(双电源)

图3-19: 双绞线接口图(双电源)

# 4.0 寄存器说明

本章介绍各种控制和状态寄存器(CSR)。所有寄存器均遵循IEEE 802.3(第22.2.4条)管理寄存器组。所有功能和位定义均符合这些标准。每个寄存器定义中均包含IEEE 802.3指定的寄存器索引(十进制),标识通过串行管理接口(SMI)协议对这些寄存器进行寻址。

### 4.1 寄存器命名法

表4-1介绍了本文档中使用的寄存器位属性标识。

表4-1: 寄存器位类型

| 寄存器位类型标识 | 寄存器位说明                                                                                                                                   |

|----------|------------------------------------------------------------------------------------------------------------------------------------------|

| R        | 读:可以对具有该属性的寄存器或位进行读操作。                                                                                                                   |

| W        | 写:可以对具有该属性的寄存器或位进行写操作。                                                                                                                   |

| RO       | <b>只读:</b> 只读。写操作不起作用。                                                                                                                   |

| WO       | <b>只写:</b> 如果寄存器或位为只写,则读操作会返回未指定的数据。                                                                                                     |

| WC       | <b>写1以清零</b> :写1可将该位清零。写零不起作用。                                                                                                           |

| WAC      | 写任意内容以清零:写入任意内容均可将该位清零。                                                                                                                  |

| RC       | <b>读取以清零</b> :内容在进行读操作后清零。写操作不起作用。                                                                                                       |

| LL       | <b>锁存低电平:</b> 读取寄存器时清零。                                                                                                                  |

| LH       | <b>锁存高电平:</b> 读取寄存器时清零。                                                                                                                  |

| SC       | <b>自行清零:内容在置1后自行清零</b> 。写零不起作用。内容可被读取。                                                                                                   |

| SS       | <b>自行置1:内容在清零后自行置1</b> 。写1不起作用。内容可被读取。                                                                                                   |

| RO/LH    | <b>只读,锁存高电平</b> :具有该属性的位在被读取前始终保持为高电平。读取该位后,如果高电平条件仍存在,则该位将保持高电平;如果高电平条件已消除,则该位将变为低电平。如果该位未被读取,则无论高电平条件是否发生变化,该位都保持高电平。一些以太网PHY寄存器使用该模式。 |

| NASR     | <b>不受软件复位影响。NASR</b> 位的状态在软件复位置为有效时不发生更改。                                                                                                |

| RESERVED | <b>保留位域:</b> 保留位域必须写入零,以确保未来的兼容性。如果读取保留位,无法保证读取到的值。                                                                                      |

其中的许多寄存器位符号可以组合使用。以下给出了一些示例:

- R/W: 可以写入。读取时将返回当前设置。

- R/WAC: 读取时将返回当前设置。写入任意内容均可将该位清零。

### 4.2 控制和状态寄存器

表4-2列出了支持的寄存器。后续几小节提供了寄存器的详细信息(包括位定义)。

表4-2: SMI寄存器映射

| 寄存器索引<br>(十进制) | 寄存器名称         | 组     |

|----------------|---------------|-------|

| 0              | 基本控制寄存器       | 基本    |

| 1              | 基本状态寄存器       | 基本    |

| 2              | PHY标识符1       | 扩展    |

| 3              | PHY标识符2       | 扩展    |

| 4              | 自动协商通告寄存器     | 扩展    |

| 5              | 自动协商链路伙伴功能寄存器 | 扩展    |

| 6              | 自动协商扩展寄存器     | 扩展    |

| 17             | 模式控制/状态寄存器    | 供应商特定 |

| 18             | 特殊模式          | 供应商特定 |

| 26             | 符号错误计数器寄存器    | 供应商特定 |

| 27             | 控制/状态指示寄存器    | 供应商特定 |

| 29             | 中断源寄存器        | 供应商特定 |

| 30             | 中断屏蔽寄存器       | 供应商特定 |

| 31             | PHY特殊控制/状态寄存器 | 供应商特定 |

### 4.2.1 基本控制寄存器

索引(十进制):0

| Bit | 说明                                                                                              | 类型        | 默认   |

|-----|-------------------------------------------------------------------------------------------------|-----------|------|

| 15  | <b>软复位</b> 1 = 软件复位。该位自行清零。将该位置1时,不要设置该寄存器中的其他位。该配置(如第3.7.2节"MODE[2:0]:模式配置"所述)通过寄存器位值而非模式引脚设置。 | R/W<br>SC | 0b   |

| 14  | <b>环回</b> 0 = 正常工作 1 = 环回模式                                                                     | R/W       | db   |

| 13  | <b>速度选择</b> 0 = 10 Mbps 1 = 100 Mbps 使能自动协商时忽略(0.12 = 1)。                                       | R/W       | 注4-1 |

| 12  | <b>自动协商使能</b> 0 = 禁止自动协商过程 1 = 使能自动协商过程(改写 <b>0.13</b> 和 <b>0.8</b> )                           | R/W       | 注4-1 |

| 11  | <b>掉电</b> 0 = 正常工作 1 = 常规掉电模式 在将掉电位置1之前,必须将自动协商使能位清零。                                           | R/W       | 0b   |

| Bit | 说明                                               | 类型        | 默认           |

|-----|--------------------------------------------------|-----------|--------------|

| 10  | <b>隔离</b><br>0 = 正常工作                            | R/W       | 0b           |

|     | 1 = PHY与RMII电气隔离                                 |           |              |

| 9   | <b>重启自动协商</b> 0 = 正常工作 1 = 重启自动协商过程 该位自行清零。      | R/W<br>SC | 0b           |

| 8   | <b>双工模式</b> 0 = 半双工 1 = 全双工 使能自动协商时忽略(0.12 = 1)。 | R/W       | 注 <b>4-1</b> |

| 7:0 | 保留                                               | RO        | _            |

**注4-1** 该位的默认值由MODE[2:0]配置脚确定。更多信息,请参见第3.7.2节"MODE[2:0]:模式配置"。

### 4.2.2 基本状态寄存器

索引(十进制):1

| Bit | 说明                                                                 | 类型 | 默认 |

|-----|--------------------------------------------------------------------|----|----|

| 15  | 100BASE-T4<br>0 = 不支持T4<br>1 = 支持T4                                | RO | 0b |

| 14  | 100BASE-TX全双工<br>0 = 不支持TX全双工<br>1 = 支持TX全双工                       | RO | 1b |

| 13  | 100BASE-TX半双工<br>0 = 不支持TX半双工<br>1 = 支持TX半双工                       | RO | 1b |

| 12  | 10BASE-T全双工<br>0 = 不支持10 Mbps全双工<br>1 = 支持10 Mbps全双工               | RO | 1b |

| 11  | 10BASE-T半双工<br>0 = 不支持10 Mbps半双工<br>1 = 支持10 Mbps半双工               | RO | 1b |

| 10  | 100BASE-T2全双工<br>0 = PHY不支持全双工100BASE-T2<br>1 = PHY支持全双工100BASE-T2 | RO | 0b |

| 9   | 100BASE-T2半双工<br>0 = PHY不支持半双工100BASE-T2<br>1 = PHY支持半双工100BASE-T2 | RO | 0b |

| 8   | 扩展状态<br>0 = 寄存器 <b>15</b> 中没有扩展状态信息<br>1 = 寄存器 <b>15</b> 中有扩展状态信息  | RO | 0b |

| Bit | 说明                                              | 类型    | 默认 |

|-----|-------------------------------------------------|-------|----|

| 7:6 | 保留                                              | RO    | _  |

| 5   | 自动协商完成<br>0=自动协商过程未完成<br>1=自动协商过程已完成            | RO    | 0b |

| 4   | 远程故障<br>1 = 已检测到远程故障状态<br>0 = 无任何远程故障           | RO/LH | 0b |

| 3   | 自动协商功能<br>0=不支持自动协商功能<br>1=支持自动协商功能             | RO    | 1b |

| 2   | <b>链路状态</b><br>0 = 链路处于断开状态<br>1 = 链路处于接通状态     | RO/LL | 0b |

| 1   | Jabber检测<br>0 = 未检测到Jabber状态<br>1 = 检测到Jabber状态 | RO/LH | 0b |

| 0   | 扩展功能<br>0=不支持扩展功能寄存器<br>1=支持扩展功能寄存器             | RO    | 1b |

### 4.2.3 PHY标识符1寄存器

索引(十进制):2

大小: 16位

| Bit  | 说明                                                                         | 类型  | 默认    |

|------|----------------------------------------------------------------------------|-----|-------|

| 15:0 | PHY ID编号<br>分配到组织惟一标识符(Organizationally Unique Identifier,OUI)的第3<br>至18位。 | R/W | 0007h |

### 4.2.4 PHY标识符2寄存器

索引(十进制):3

| Bit   | 说明                          | 类型  | 默认      |

|-------|-----------------------------|-----|---------|

| 15:10 | PHY ID编号<br>分配到OUI的第19至24位。 | R/W | 110000b |

| 9:4   | 型号编号<br>制造商的六位型号。           | R/W | 001111b |

| 3:0   | 版本号制造商的四位版本号。               | R/W | 注4-2    |

注4-2 该字段的默认值因芯片版本号而异。

### 4.2.5 自动协商通告寄存器

索引(十进制):4

大小: 16位

| Bit   | 说明                                                                                                                     | 类型  | 默认     |

|-------|------------------------------------------------------------------------------------------------------------------------|-----|--------|

| 15:14 | 保留                                                                                                                     | RO  | _      |

| 13    | 远程故障<br>0 = 无任何远程故障                                                                                                    | R/W | 0b     |

|       | 1 = 检测到远程故障                                                                                                            |     |        |

| 12    | 保留                                                                                                                     | RO  | _      |

| 11:10 | <b>暂停工作</b> 00 = 无暂停 01 = 对称暂停 10 = 面向链路伙伴的非对称暂停 11 = 通告支持面向本地设备的对称暂停和非对称暂停 注: 即使同时设置了对称暂停和非对称暂停,器件在自动协商完成后也只能配置为其中之一。 | R/W | 00b    |

| 9     | 保留                                                                                                                     | RO  | _      |

| 8     | 100BASE-TX全双工<br>0 = 不支持TX全双工<br>1 = 支持TX全双工                                                                           | R/W | 注4-3   |

| 7     | 100BASE-TX<br>0 = 不支持TX<br>1 = 支持TX                                                                                    | R/W | 1b     |

| 6     | 10BASE-T全双工<br>0 = 不支持10 Mbps全双工<br>1 = 支持10 Mbps全双工                                                                   | R/W | 注4-3   |

| 5     | 10BASE-T<br>0 = 不支持10 Mbps<br>1 = 支持10 Mbps                                                                            | R/W | 注4-3   |

| 4     | 选择器位域<br>00001 = IEEE 802.3                                                                                            | R/W | 00001b |

**注4-3** 该位的默认值由MODE[2:0]配置脚确定。更多信息,请参见第3.7.2节"MODE[2:0]:模式配置"。

### 4.2.6 自动协商链路伙伴功能寄存器

索引 (十进制):5

| Bit   | 说明                                   | 类型   | 默认     |

|-------|--------------------------------------|------|--------|

| 15    | 下一页                                  | RO   | 0b     |

|       | 0 = 不支持下一页 1 = 支持下一页                 |      |        |

|       | <b>注:</b> 该器件不支持下一页功能。               |      |        |

| 14    | 应答                                   | RO   | 0b     |

|       | 0 = 尚未接收到链路代码字<br>1 = 已从链路伙伴接收到链路代码字 |      |        |

| 13    | 远程故障                                 | RO   | 0b     |

|       | 0 = 无任何远程故障<br>1 = 检测到远程故障           |      |        |

| 12:11 | 保留                                   | RO   | _      |

| 10    | 暂停工作                                 | RO   | 0b     |

|       | 0 = 伙伴站点不支持暂停<br>1 = 伙伴站点支持暂停        |      |        |

| 9     | 100BASE-T4                           | RO   | 0b     |

|       | 0 = 不支持T4                            | 110  |        |

|       | 1 = 支持T4                             |      |        |

|       | 注: 该器件不支持T4功能。                       |      | 0b     |

| 8     | 100BASE-TX全双工<br>0 = 不支持TX全双工        | RO   | au     |

|       | 1 = 支持TX全双工                          |      |        |

| 7     | 100BASE-TX                           | RO   | 0b     |

|       | 0 = 不支持TX                            |      |        |

| 6     | 1 = 支持TX<br>10BASE-T全双工              | RO   | 0b     |

| 0     | 10BASE-1至XX工<br>  0 = 不支持10 Mbps全双工  | RO . | OD     |

|       | 1 = 支持10 Mbps全双工                     |      |        |

| 5     | 10BASE-T                             | RO   | 0b     |

|       | 0 = 不支持10 Mbps<br>1 = 支持10 Mbps      |      |        |

| 4:0   | 1 = 又行10 Mbps<br> 选择器位域              | RO   | 00001b |

| 4.0   | 近洋衛世域<br>  00001 = IEEE 802.3        | , KO | 000015 |

| L     | 1                                    | l .  | 1      |

### 4.2.7 自动协商扩展寄存器

索引(十进制):6

大小: 16位

| Bit  | 说明                                                     | 类型    | 默认 |

|------|--------------------------------------------------------|-------|----|

| 15:5 | 保留                                                     | RO    | _  |

| 4    | 并行检测故障<br>0=并行检测逻辑未检测到故障<br>1=并行检测逻辑已检测到故障             | RO/LH | 0b |

| 3    | <b>链路伙伴下一页功能</b> 0 = 链路伙伴不支持下一页功能 1 = 链路伙伴支持下一页功能      | RO    | 0b |

| 2    | 下一页功能<br>0=本地设备不支持下一页功能<br>1=本地设备支持下一页功能               | RO    | 0b |

| 1    | 页接收<br>0 = 尚未接收到新页<br>1 = 已接收到新页                       | RO/LH | 0b |

| 0    | <b>链路伙伴自动协商功能</b><br>0=链路伙伴不支持自动协商功能<br>1=链路伙伴支持自动协商功能 | RO    | 0b |

### 4.2.8 模式控制/状态寄存器

索引(十进制):17

| Bit   | 说明                                                                                                                                         | 类型  | 默认 |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------|-----|----|

| 15:14 | 保留                                                                                                                                         | RO  | _  |

| 13    | EDPWRDOWN         使能电能检测掉电模式:         0 = 禁止电能检测掉电         1 = 使能电能检测掉电                                                                    | R/W | 0b |

| 12:10 | 保留                                                                                                                                         | RO  | _  |

| 9     | FARLOOPBACK<br>使能远端环回模式(例如,同时发回所有接收的数据包(仅限100BASE-TX))。即使隔离位(0.10)置1,也可以使用该模式。<br>0 = 禁止远端环回模式<br>1 = 使能远端环回模式<br>更多信息,请参见第3.8.8.2节"远端环回"。 | R/W | 0b |

| 8:7   | 保留                                                                                                                                         | RO  | _  |

| 6     | ALTINT<br>备用中断模式:<br>0 = 使能主要中断系统(默认)<br>1 = 使能备用中断系统<br>更多信息,请参见第3.6节"中断管理"。                                                              | R/W | 0b |

| Bit | 说明                                                                                                                | 类型  | 默认 |

|-----|-------------------------------------------------------------------------------------------------------------------|-----|----|

| 5:2 | 保留                                                                                                                | RO  | _  |

| 1   | <b>ENERGYON</b><br>指示是否检测到电能。如果在256 ms内未检测到有效电能,则该位转<br>换为0。该位通过硬件复位复位为1,不受软件复位的影响。更多信息,<br>请参见第3.8.3.2节"电能检测掉电"。 | RO  | 1b |

| 0   | 保留                                                                                                                | R/W | d0 |

### 4.2.9 特殊模式寄存器

索引(十进制): 18

大小: 16位

| Bit  | 说明                                                                           | 类型          | 默认           |

|------|------------------------------------------------------------------------------|-------------|--------------|

| 15   | 保留                                                                           | RO          | _            |

| 14   | 保留<br>写为1,读取时忽略。                                                             | R/W<br>NASR | 1b           |

| 13:8 | 保留                                                                           | RO          | _            |

| 7:5  | MODE 收发器的工作模式。更多详细信息,请参见第3.7.2节"MODE[2:0]:模式配置"。                             | R/W<br>NASR | 注 <b>4-4</b> |

| 4:0  | PHYAD PHY地址。PHY地址用于SMI地址以及初始化加密(加扰器)密钥。更多详细信息,请参见第3.7.1节"PHYAD[0]: PHY地址配置"。 | R/W<br>NASR | 注4-5         |

注4-4 该位域的默认值由MODE[2:0]配置脚确定。更多信息,请参见第3.7.2节"MODE[2:0]:模式配置"。

注4-5 该位域的默认值由PHYAD[0]配置脚确定。更多信息,请参见第3.7.1节 "PHYAD[0]: PHY地址配置"。

### 4.2.10 符号错误计数器寄存器

索引(十进制): 26

| Bit  | 说明                                                                                                                                                                                                                       | 类型 | 默认    |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-------|

| 15:0 | SYM_ERR_CNT<br>只要在100BASE-TX模式下接收到无效的代码符号(包括空闲符号),<br>该符号错误计数器就会递增。即使接收到的数据包中包含多个符号错<br>误,计数器也只针对每个数据包递增一次。该计数器可向上递增到<br>65536(2 <sup>16</sup> ),并在达到最大值后计满返回到0。<br>注: 该寄存器在复位时清零,而非通过读取该寄存器来清零。该寄存<br>器在10BASE-T模式下不递增。 | RO | 0000h |

### 4.2.11 特殊控制/状态指示寄存器

索引 (十进制): 27 大小: 16位

| Bit  | 说明                                                                | 类型          | 默认 |

|------|-------------------------------------------------------------------|-------------|----|

| 15   | AMDIXCTRL HP自动MDIX控制: 0 = 使能自动MDIX 1 = 禁止自动MDIX(使用27.13来控制通道)     | R/W         | d0 |

| 14   | 保留                                                                | RO          |    |

| 13   | CH_SELECT<br>手动通道选择:<br>0 = MDI(TX发送,RX接收)<br>1 = MDIX(TX接收,RX发送) | R/W         | d0 |

| 12   | 保留                                                                | RO          | _  |

| 11   | SQEOFF<br>禁止SQE测试(心跳):<br>0 = 使能SQE测试<br>1 = 禁止SQE测试              | R/W<br>NASR | 0b |

| 10.5 | 保留                                                                | RO          | _  |

| 4    | XPOL         10BASE-T的极性状态:         0 = 正常极性         1 = 相反极性     | RO          | 0b |

| 3.0  | 保留                                                                | RO          | _  |

### 4.2.12 中断源标志寄存器

索引(十进制): 29

| Bit  | 说明                                      | 类型    | 默认 |

|------|-----------------------------------------|-------|----|

| 15:8 | 保留                                      | RO    | _  |

| 7    | INT7<br>0 = 不是中断源<br>1 = 产生ENERGYON     | RO/LH | 0b |

| 6    | INT6<br>0 = 不是中断源<br>1 = 自动协商完成         | RO/LH | 0b |

| 5    | INT5<br>0 = 不是中断源<br>1 = 检测到远程故障        | RO/LH | 0b |

| 4    | INT4<br>0 = 不是中断源<br>1 = 链接断开(链路状态置为无效) | RO/LH | 0b |

| Bit | 说明                                 | 类型    | 默认 |

|-----|------------------------------------|-------|----|

| 3   | INT3<br>0 = 不是中断源<br>1 = 自动协商LP应答  | RO/LH | db |

| 2   | INT2<br>0 = 不是中断源<br>1 = 并行检测故障    | RO/LH | 0b |

| 1   | INT1<br>0 = 不是中断源<br>1 = 接收到自动协商页面 | RO/LH | 0b |

| 0   | 保留                                 | RO    | 0b |

### 4.2.13 中断屏蔽寄存器

索引(十进制):30

大小: 16位

| Bit  | 说明                                                                           | 类型  | 默认       |

|------|------------------------------------------------------------------------------|-----|----------|

| 15:8 | 保留                                                                           | RO  | _        |

| 7:1  | 屏蔽位<br>0 = 屏蔽中断源<br>1 = 允许中断源<br>注: 有关相应中断定义的详细信息,请参见第4.2.12节"中断源标志<br>寄存器"。 | R/W | 0000000b |

| 0    | 保留                                                                           | RO  | _        |

# 4.2.14 PHY特殊控制/状态寄存器

索引(十进制):31

| Bit   | 说明                                                                                                  | 类型  | 默认       |

|-------|-----------------------------------------------------------------------------------------------------|-----|----------|

| 15:13 | 保留                                                                                                  | RO  | _        |

| 12    | 自动完成<br>自动协商完成指示:<br>0=自动协商未完成或已禁止(或未激活)<br>1=自动协商已完成                                               | RO  | 0b       |

| 11:5  | 保留——写为0000010b,读取时忽略。                                                                               | R/W | 0000010b |

| 4:2   | 速度指示 HCDSPEED值: 001 = 10BASE-T半双工模式 101 = 10BASE-T全双工模式 010 = 100BASE-TX半双工模式 110 = 100BASE-TX全双工模式 | RO  | XXX      |

| 1:0   | 保留                                                                                                  | RO  | _        |

# 5.0 工作特性

### 5.1 绝对最大额定值\*

|        | 云(VDDIO、VDD1A和VDD2A)(注5-1)                                                                                                      |

|--------|---------------------------------------------------------------------------------------------------------------------------------|

|        | 亥电源电压(VDDCR)(注5-1)                                                                                                              |

| 以太网磁   | 兹件电源电压0.5V至+3.6V                                                                                                                |

| 信号引肽   | 印相对于地的正电压( <u>注5-2</u> )+6V                                                                                                     |

|        | 即相对于地的负电压( <u>注5-3)</u>                                                                                                         |

|        | .KIN相对于地的正电压+3.6V                                                                                                               |

|        | 对于地的正电压+2.5V                                                                                                                    |

| 静止空气   | 〔中的工作环境温度(T <sub>A</sub> )注5-4                                                                                                  |

| 存储温度   | ₹55°C至+150°C                                                                                                                    |

| 引脚温度   | 要范围请参见JEDEC规范J-STD-020                                                                                                          |

| 符合JEDE | EC JESD22-A114标准的HBM ESD性能等级3A                                                                                                  |

|        | D-4-2接触放电ESD性能(注5-5)+/-8 kV                                                                                                     |

|        | )-4-2气隙放电ESD性能(注5-5)+/-15 kV                                                                                                    |

| 符合EIA/ | 'JESD 78标准的闩锁性能+/-150 mA                                                                                                        |

| 注5-1   | 通过实验室或系统电源为此器件供电时,务必保证不要超过绝对最大额定值,否则可能导致器件出现<br>故障。接通或关断交流电源时,某些电源的输出端会出现电压尖峰。此外,交流电源线上的电压瞬变<br>可能会出现在直流输出上。如果存在这种可能性,建议使用钳位电路。 |

| 注5-2   | 该额定值不适用于以下引脚: XTAL1/CLKIN、XTAL2和RBIAS。                                                                                          |

| 注5-3   | 该额定值不适用于以下引脚: RBIAS。                                                                                                            |

| 注5-4   | 扩展商业级温度范围为0°C至+85°C。                                                                                                            |

<sup>\*</sup>如果器件的工作条件超过上述绝对最大额定值,可能对器件造成永久性损坏。上述值仅代表本规范规定的极限工作条件。器件长时间工作在最大值条件下,其可靠性可能受到影响。我们无法保证器件在超过第5.2节"工作条件\*\*"、第5.1节"绝对最大额定值\*"或本规范任何其他适用章节中规定的最大值条件下仍可正常工作。请注意,除非另行说明,否则器件信号不耐5V电压。

### 5.2 工作条件\*\*

注5-5

| 电源电压(VDDIO)+1.62V至+3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | .6V |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 模拟端口电源电压(VDD1A和VDD2A)+3.0V至+3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | .6V |

| 数字内核电源电压(VDDCR)+1.08V至+1.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 32V |

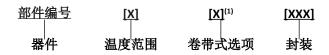

| 以太网磁件电源电压+2.25V至+3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | .6V |